专利摘要

本发明公开了一种模拟数字混合结构的锁相放大器及其锁相放大方法,该锁相放大器包括输入信号处理系统、参考信号产生系统、模拟处理系统、模数转换系统及数字处理系统,参考信号产生系统的第一输出端和第二输出端输出两路相互正交的正弦波参考信号,模拟处理系统包括两个模拟乘法器和模拟低通滤波器,数字处理系统包括两个数字低通滤波器和数字运算器。本锁相放大器在检测信号过程中允许混叠信号的存在,然后通过模拟低通滤波器和数字低通滤波器的组合,可以有效滤除输入信号中的干扰信号,并滤除高频干扰信号和混叠信号,可以实现对各种频率信号的检测,有效地提高了信噪比,降低了硬件要求,生产成本较低,可广泛应用于弱信号测量领域中。

权利要求

1.一种模拟数字混合结构的锁相放大器,其特征在于,包括输入信号处理系统(100)、参考信号产生系统(200)、模拟处理系统(300)、模数转换系统(400)及数字处理系统(500),所述参考信号产生系统(200)的第一输出端和第二输出端输出两路相互正交的正弦波参考信号;

所述模拟处理系统(300)包括第一模拟乘法器(31)、第二模拟乘法器(32)、第一模拟低通滤波器(41)及第二模拟低通滤波器(42),所述模数转换系统(400)包括第一模数转换器(51)及第二模数转换器(52),所述数字处理系统(500)包括第一数字低通滤波器(61)、第二数字低通滤波器(62)及数字运算器(7);

所述输入信号处理系统(100)的输入端接输入信号,输出端分别与第一模拟乘法器(31)的第一输入端和第二模拟乘法器(32)的第一输入端连接,所述参考信号产生系统(200)的第一输出端与第一模拟乘法器(31)的第二输入端连接,所述参考信号产生系统(200)的第二输出端与第二模拟乘法器(32)的第二输入端连接;

所述第一模拟乘法器(31)的输出信号依次通过第一模拟低通滤波器(41)、第一模数转换器(51)及第一数字低通滤波器(61)输入到数字运算器(7),所述第二模拟乘法器(32)的输出信号依次通过第二模拟低通滤波器(42)、第二模数转换器(52)及第二数字低通滤波器(62)输入到数字运算器(7)。

2.根据权利要求1所述的一种模拟数字混合结构的锁相放大器,其特征在于,所述数字运算器(7)包括幅值计算模块(71)、相位计算模块(72)、误差校正模块(73)和反馈模块(74),所述第一数字低通滤波器(61)和第二数字低通滤波器(62)所输出的信号均分别输入到幅值计算模块(71)、相位计算模块(72)、误差校正模块(73)及反馈模块(74),所述反馈模块(74)的输出端与参考信号产生系统(200)的输入端连接。

3.根据权利要求2所述的一种模拟数字混合结构的锁相放大器,其特征在于,所述输入信号处理系统(100)包括依次串联的缓冲转换模块(11)、滤波模块(12)和放大模块(13),缓冲转换模块(11)的输入端接输入信号,用于对输入信号进行缓冲或信号转换,放大模块(13)的输出端分别与第一模拟乘法器(31)的第一输入端和第二模拟乘法器(32)的第一输入端连接。

4.根据权利要求2所述的一种模拟数字混合结构的锁相放大器,其特征在于,参考信号产生系统(200)包括相位累加模块(21)和信号发生模块(22),所述反馈模块(74)的输出端与相位累加模块(21)的输入端连接,所述相位累加模块(21)的输出端与信号发生模块(22)的输入端连接,所述信号发生模块(22)的第一输出端与第一模拟乘法器(31)的第二输入端连接,第二输出端与第二模拟乘法器(32)的第二输入端连接。

5.根据权利要求3所述的一种模拟数字混合结构的锁相放大器,其特征在于,所述输入信号为电流信号,所述缓冲转换模块(11)包括输入耦合电路、电流-电压转换电路及差分放大电路,所述输入耦合电路的输入端接输入信号,输出端依次通过电流-电压转换电路及差分放大电路后与滤波模块(12)连接。

6.根据权利要求3所述的一种模拟数字混合结构的锁相放大器,其特征在于,所述输入信号为电压信号,所述缓冲转换模块(11)包括输入耦合电路及差分放大电路,所述输入耦合电路的输入端接输入信号,输出端通过差分放大电路与滤波模块(12)连接。

7.根据权利要求3所述的一种模拟数字混合结构的锁相放大器,其特征在于,所述滤波模块(12)包括50Hz/100Hz陷波器和自跟踪窄带滤波器,所述缓冲转换模块(11)依次通过50Hz/100Hz陷波器、自跟踪窄带滤波器和放大模块(13)连接。

8.一种模拟数字混合结构的锁相放大器的锁相放大方法,其特征在于,包括:

S1、通过参考信号产生系统产生两路相互正交的正弦波信号,然后将两路相互正交的正弦波信号分别与输入信号相乘后,得到两路模拟电压输出信号;

S2、分别将该两路模拟电压输出信号进行模拟低通滤波后,进行模数转换,得到两路数字电压输出信号;

S3、分别对两路数字电压输出信号进行数字低通滤波,并滤除高频干扰信号和混叠信号后,将两路滤波后的输出信号发送到数字运算器。

9.根据权利要求8所述的一种模拟数字混合结构的锁相放大器的锁相放大方法,其特征在于,在所述步骤S3之后还包括以下步骤:

S4、数字运算器接收该两路滤波后的输出信号后,计算获得输入信号中待测信号的幅值及相位,并校正由模拟运算所带来的误差,同时将获得的待测信号的相位反馈到参考信号产生系统。

10.根据权利要求9所述的一种模拟数字混合结构的锁相放大器的锁相放大方法,其特征在于,在所述步骤S1之前还包括以下步骤:

S01、将输入信号进行缓冲,若输入信号是电流信号,则同时将其转换为电压信号;

S02、将缓冲后的输入信号依次进行滤波及信号放大。

说明书

技术领域

本发明涉及锁相放大器领域,特别是涉及一种模拟数字混合结构的锁相放大器。

背景技术

锁相放大器,Lock-in Amplifier,英文缩写为LIA,是一种对弱信号进行相敏检波的放大器,它利用和被测信号有相同频率和相位关系的参考信号作为比较基准,只对被测信号中那些与参考信号同频或倍频的噪声分量有响应,能大幅度抑制噪声,改善检测的信噪比。锁相放大器的基本原理框图如图1所示,其中相敏检测器通常由乘法器和积分器组成,而积分器通常采用低通滤波器,图1中锁相放大器采用互相关检测原理,其基本工作原理如下:

根据互相关函数的定义,假设输入信号为x(t)=S(t)+n(t),参考信号为y(t)。其中S(t)为待测信号,n(t)为噪声信号。则输入信号与参考信号的互相关函数为:

根据互相关函数的特性,噪声信号n(t)与参考信号y(t)不相关,则有Rny(τ)=0,若选择的参考信号y(t)与待测信号S(t)是互相关的,则可以得到输入信号与参考信号的互相关运算的输出为:

Rxy(τ)=Rsy(τ)

由此可知,锁相放大器可以实现微弱信号提取,从而去除输入信号中的噪声信号,提高输出信号的信噪比。

目前,锁相放大器主要分两大类,模拟锁相放大器(简称ALIA)和数字锁相放大器(简称DLIA)。模拟锁相放大器,其实现锁相放大的核心算法利用模拟电子器件实现,即其相敏检测器完全由模拟乘法器和模拟低通滤波器组成,如图2所示。由于模拟电子器件存在温度漂移,而且各个模拟有源滤波器本身也是噪声源,这些有源滤波器的噪声会影响到模拟锁相放大器提高输出信噪比的性能,而且模拟锁相放大器本身是个开环系统,无法对干扰造成的误差予以纠正,滤波特性一般。

而数字锁相放大器则是利用模数转换器将模拟输入信号提取成数字序列,然后利用数字系统的软件实现锁相放大中的乘法和积分算法,如图3所示。与模拟锁相放大器相比,数字锁相放大器由于在输出通道中没有直流放大器,可以避免直流放大器的工作特性随时间变化的不稳定性和由于温度变化引起的温度漂移带来的干扰。但是,由于按照采样定理,其采用的模数转换器的采样速率必须至少大于最高信号频率的两倍,加上其受到数字部分的处理部件的运算能力的限制,数字锁相放大器通常只能应用于低频信号的检测中,对于较高频率例如MHz以上频率的信号,数字锁相放大器较难实现检测或者能实现检测但是成本极高。

发明内容

为了解决上述的技术问题,本发明的目的是提供一种模拟数字混合结构的锁相放大器,本发明的另一目的是提供一种模拟数字混合结构的锁相放大器的锁相放大方法。

本发明解决其技术问题所采用的技术方案是:

一种模拟数字混合结构的锁相放大器,包括输入信号处理系统、参考信号产生系统、模拟处理系统、模数转换系统及数字处理系统,所述参考信号产生系统的第一输出端和第二输出端输出两路相互正交的正弦波参考信号;

所述模拟处理系统包括第一模拟乘法器、第二模拟乘法器、第一模拟低通滤波器及第二模拟低通滤波器,所述模数转换系统包括第一模数转换器及第二模数转换器,所述数字处理系统包括第一数字低通滤波器、第二数字低通滤波器及数字运算器;

所述输入信号处理系统的输入端接输入信号,输出端分别与第一模拟乘法器的第一输入端和第二模拟乘法器的第一输入端连接,所述参考信号产生系统的第一输出端与第一模拟乘法器的第二输入端连接,所述参考信号产生系统的第二输出端与第二模拟乘法器的第二输入端连接;

所述第一模拟乘法器的输出信号依次通过第一模拟低通滤波器、第一模数转换器及第一数字低通滤波器输入到数字运算器,所述第二模拟乘法器的输出信号依次通过第二模拟低通滤波器、第二模数转换器及第二数字低通滤波器输入到数字运算器。

进一步,所述数字运算器包括幅值计算模块、相位计算模块、误差校正模块和反馈模块,所述第一数字低通滤波器和第二数字低通滤波器所输出的信号均分别输入到幅值计算模块、相位计算模块、误差校正模块及反馈模块,所述反馈模块的输出端与参考信号产生系统的输入端连接。

进一步,所述输入信号处理系统包括依次串联的缓冲转换模块、滤波模块和放大模块,缓冲转换模块的输入端接输入信号,用于对输入信号进行缓冲或信号转换,放大模块的输出端分别与第一模拟乘法器的第一输入端和第二模拟乘法器的第一输入端连接。

进一步,参考信号产生系统包括相位累加模块和信号发生模块,所述反馈模块的输出端与相位累加模块的输入端连接,所述相位累加模块的输出端与信号发生模块的输入端连接,所述信号发生模块的第一输出端与第一模拟乘法器的第二输入端连接,第二输出端与第二模拟乘法器的第二输入端连接。

进一步,所述输入信号为电流信号,所述缓冲转换模块包括输入耦合电路、电流-电压转换电路及差分放大电路,所述输入耦合电路的输入端接输入信号,输出端依次通过电流-电压转换电路及差分放大电路后与滤波模块连接。

进一步,所述输入信号为电压信号,所述缓冲转换模块包括输入耦合电路及差分放大电路,所述输入耦合电路的输入端接输入信号,输出端通过差分放大电路与滤波模块连接。

进一步,所述滤波模块包括50Hz/100Hz陷波器和自跟踪窄带滤波器,所述缓冲转换模块依次通过50Hz/100Hz陷波器、自跟踪窄带滤波器和放大模块连接。

本发明解决其技术问题所采用的另一技术方案是:

一种模拟数字混合结构的锁相放大器的锁相放大方法,包括:

S1、通过参考信号产生系统产生两路相互正交的正弦波信号,然后将两路相互正交的正弦波信号分别与输入信号相乘后,得到两路模拟电压输出信号;

S2、分别将该两路模拟电压输出信号进行模拟低通滤波后,进行模数转换,得到两路数字电压输出信号;

S3、分别对两路数字电压输出信号进行数字低通滤波,并滤除高频干扰信号和混叠信号后,将两路滤波后的输出信号发送到数字运算器。

进一步,在所述步骤S3之后还包括以下步骤:

S4、数字运算器接收该两路滤波后的输出信号后,计算获得输入信号中待测信号的幅值及相位,并校正由模拟运算所带来的误差,同时将获得的待测信号的相位反馈到参考信号产生系统。

进一步,在所述步骤S1之前还包括以下步骤:

S01、将输入信号进行缓冲,若输入信号是电流信号,则同时将其转换为电压信号;

S02、将缓冲后的输入信号依次进行滤波及信号放大。

本发明的有益效果是:本发明的一种模拟数字混合结构的锁相放大器,包括输入信号处理系统、参考信号产生系统、模拟处理系统、模数转换系统及数字处理系统,参考信号产生系统的第一输出端和第二输出端输出两路相互正交的正弦波参考信号,模拟处理系统包括两个模拟乘法器和模拟低通滤波器,数字处理系统包括两个数字低通滤波器和数字运算器。本发明通过将输入信号与两路参考信号分别通过模拟乘法器进行乘法运算后,依次进行模拟低通滤波、模数转换以及数字低通滤波后发送到数字运算器,信号检测过程中允许混叠信号的存在,然后通过模拟低通滤波器和数字低通滤波器的组合,可以有效滤除输入信号中的干扰信号,并滤除高频干扰信号和混叠信号,可以实现对各种频率信号的检测,克服了现有技术中的模拟锁相放大器和数字锁相放大器的缺陷,而且有效地提高了本锁相放大器检测结果的信噪比。另外,本锁相放大器降低了对模拟低通滤波器的硬件要求,加上其在乘法运算以及模拟低通滤波后进行模数转换,大大降低了对模数转换系统的采样速率的要求,因此本锁相放大器降低了硬件要求,生产成本较低。

另外,数字运算器包括幅值计算模块、相位计算模块、误差校正模块和反馈模块,可计算出输入信号中待测信号的幅值及相位,同时进行误差校正,并通过反馈模块将待测信号的相位反馈到参考信号产生系统,参考信号产生系统可根据获得的待测信号的相位实时调节所产生的两路相互正交的正弦波参考信号的相位值,克服了现有技术中的模拟锁相放大器的开环系统结构所带来的缺陷,有效地提高了本锁相放大器中相位检测的分辨率和精度。

本发明的另一有益效果是:本发明的一种模拟数字混合结构的锁相放大器的锁相放大方法,通过参考信号产生系统产生两路相互正交的正弦波信号,然后将两路相互正交的正弦波信号分别与输入信号相乘后,得到两路模拟电压输出信号后,分别将该两路模拟电压输出信号进行模拟低通滤波后,进行模数转换,得到两路数字电压输出信号,最后分别对两路数字电压输出信号进行数字低通滤波,并滤除高频干扰信号和混叠信号后,将两路滤波后的输出信号发送到数字运算器。本锁相放大方法通过将输入信号与两路相互正交的正弦波信号分别通过模拟乘法器进行乘法运算后,依次进行模拟低通滤波、模数转换以及数字低通滤波后发送到数字运算器,在运算过程中允许混叠信号的存在,然后通过模拟低通滤波器和数字低通滤波器的组合,可以有效滤除输入信号中的干扰信号,并滤除高频干扰信号和混叠信号,可以实现对各种频率信号的检测,而且有效地提高了检测结果的信噪比。

另外,数字运算器接收滤波后的输出信号,计算获得输入信号中待测信号的幅值及相位。本锁相放大方法将获得的待测信号的相位反馈到参考信号产生系统,参考信号产生系统可根据获得的待测信号的相位实时调节所产生的两路相互正交的正弦波信号的相位值,克服了现有技术中的模拟锁相放大器的开环系统结构所带来的缺陷,有效地提高了锁相放大时相位检测的分辨率和精度。

附图说明

下面结合附图和实施例对本发明作进一步说明。

图1是现有技术中锁相放大器的基本结构图;

图2是现有技术中模拟锁相放大器的结构框图;

图3是现有技术中数字锁相放大器的结构框图;

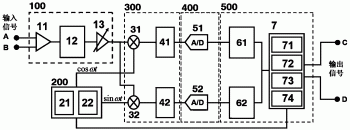

图4是本发明的一种模拟数字混合结构的锁相放大器的结构框图;

图5是存在较大干扰信号时现有技术中模拟锁相放大器进行乘法运算前后的信号变化示意图;

图6是存在较大干扰信号时本发明的锁相放大器进行乘法运算前后的信号变化示意图。

具体实施方式

参照图4,本发明提供了一种模拟数字混合结构的锁相放大器,包括输入信号处理系统100、参考信号产生系统200、模拟处理系统300、模数转换系统400及数字处理系统500,所述参考信号产生系统200的第一输出端和第二输出端输出两路相互正交的正弦波参考信号;

所述模拟处理系统300包括第一模拟乘法器31、第二模拟乘法器32、第一模拟低通滤波器41及第二模拟低通滤波器42,所述模数转换系统400包括第一模数转换器51及第二模数转换器52,所述数字处理系统500包括第一数字低通滤波器61、第二数字低通滤波器62及数字运算器7;

所述输入信号处理系统100的输入端接输入信号,输出端分别与第一模拟乘法器31的第一输入端和第二模拟乘法器32的第一输入端连接,所述参考信号产生系统200的第一输出端与第一模拟乘法器31的第二输入端连接,所述参考信号产生系统200的第二输出端与第二模拟乘法器32的第二输入端连接;

所述第一模拟乘法器31的输出信号依次通过第一模拟低通滤波器41、第一模数转换器51及第一数字低通滤波器61输入到数字运算器7,所述第二模拟乘法器32的输出信号依次通过第二模拟低通滤波器42、第二模数转换器52及第二数字低通滤波器62输入到数字运算器7。

进一步作为优选的实施方式,所述数字运算器7包括幅值计算模块71、相位计算模块72、误差校正模块73和反馈模块74,所述第一数字低通滤波器61和第二数字低通滤波器62所输出的信号均分别输入到幅值计算模块71、相位计算模块72、误差校正模块73及反馈模块74,所述反馈模块74的输出端与参考信号产生系统200的输入端连接。

进一步作为优选的实施方式,所述输入信号处理系统100包括依次串联的缓冲转换模块11、滤波模块12和放大模块13,缓冲转换模块11的输入端接输入信号,用于对输入信号进行缓冲或信号转换,放大模块13的输出端分别与第一模拟乘法器31的第一输入端和第二模拟乘法器32的第一输入端连接。

进一步作为优选的实施方式,参考信号产生系统200包括相位累加模块21和信号发生模块22,所述反馈模块74的输出端与相位累加模块21的输入端连接,所述相位累加模块21的输出端与信号发生模块22的输入端连接,所述信号发生模块22的第一输出端与第一模拟乘法器31的第二输入端连接,第二输出端与第二模拟乘法器32的第二输入端连接。

进一步作为优选的实施方式,所述输入信号为电流信号,所述缓冲转换模块11包括输入耦合电路、电流-电压转换电路及差分放大电路,所述输入耦合电路的输入端接输入信号,输出端依次通过电流-电压转换电路及差分放大电路后与滤波模块12连接。

进一步作为优选的实施方式,所述输入信号为电压信号,所述缓冲转换模块11包括输入耦合电路及差分放大电路,所述输入耦合电路的输入端接输入信号,输出端通过差分放大电路与滤波模块12连接。

进一步作为优选的实施方式,所述滤波模块12包括50Hz/100Hz陷波器和自跟踪窄带滤波器,所述缓冲转换模块11依次通过50Hz/100Hz陷波器、自跟踪窄带滤波器和放大模块13连接。

本发明还提供了一种模拟数字混合结构的锁相放大器的锁相放大方法,包括:

S1、通过参考信号产生系统产生两路相互正交的正弦波信号,然后将两路相互正交的正弦波信号分别与输入信号相乘后,得到两路模拟电压输出信号;

S2、分别将该两路模拟电压输出信号进行模拟低通滤波后,进行模数转换,得到两路数字电压输出信号;

S3、分别对两路数字电压输出信号进行数字低通滤波,并滤除高频干扰信号和混叠信号后,将两路滤波后的输出信号发送到数字运算器。

进一步作为优选的实施方式,在所述步骤S3之后还包括以下步骤:

S4、数字运算器接收该两路滤波后的输出信号后,计算获得输入信号中待测信号的幅值及相位,并校正由模拟运算所带来的误差,同时将获得的待测信号的相位反馈到参考信号产生系统。

进一步作为优选的实施方式,在所述步骤S1之前还包括以下步骤:

S01、将输入信号进行缓冲,若输入信号是电流信号,则同时将其转换为电压信号;

S02、将缓冲后的输入信号依次进行滤波及信号放大。

下面结合具体实施方式对本发明做进一步说明。

实施例一

参照图4,一种模拟数字混合结构的锁相放大器,包括输入信号处理系统100、参考信号产生系统200、模拟处理系统300、模数转换系统400及数字处理系统500,参考信号产生系统200的第一输出端和第二输出端输出两路相互正交的正弦波参考信号;

模拟处理系统300包括第一模拟乘法器31、第二模拟乘法器32、第一模拟低通滤波器41及第二模拟低通滤波器42,模数转换系统400包括第一模数转换器51及第二模数转换器52,数字处理系统500包括第一数字低通滤波器61、第二数字低通滤波器62及数字运算器7;

输入信号处理系统100的输入端接输入信号,输出端分别与第一模拟乘法器31的第一输入端和第二模拟乘法器32的第一输入端连接,参考信号产生系统200的第一输出端与第一模拟乘法器31的第二输入端连接,参考信号产生系统200的第二输出端与第二模拟乘法器32的第二输入端连接;

第一模拟乘法器31的输出信号依次通过第一模拟低通滤波器41、第一模数转换器51及第一数字低通滤波器61输入到数字运算器7,第二模拟乘法器32的输出信号依次通过第二模拟低通滤波器42、第二模数转换器52及第二数字低通滤波器62输入到数字运算器7。

数字运算器7包括幅值计算模块71、相位计算模块72、误差校正模块73和反馈模块74,第一数字低通滤波器61和第二数字低通滤波器62所输出的信号均分别输入到幅值计算模块71、相位计算模块72、误差校正模块73及反馈模块74,反馈模块74的输出端与参考信号产生系统200的输入端连接。

参考信号产生系统200包括相位累加模块21和信号发生模块22,反馈模块74的输出端与相位累加模块21的输入端连接,相位累加模块21的输出端与信号发生模块22的输入端连接,信号发生模块22的第一输出端与第一模拟乘法器31的第二输入端连接,第二输出端与第二模拟乘法器32的第二输入端连接。

本实施例中,输入信号处理系统100包括依次串联的缓冲转换模块11、滤波模块12和放大模块13,缓冲转换模块11的输入端接输入信号,用于对输入信号进行缓冲或信号转换,放大模块13的输出端分别与第一模拟乘法器31的第一输入端和第二模拟乘法器32的第一输入端连接。

若输入信号为电流信号,缓冲转换模块11包括输入耦合电路、电流-电压转换电路及差分放大电路,输入耦合电路的输入端接输入信号,输出端依次通过电流-电压转换电路及差分放大电路后与滤波模块12连接。若输入信号为电压信号,缓冲转换模块11包括输入耦合电路及差分放大电路,输入耦合电路的输入端接输入信号,输出端通过差分放大电路与滤波模块12连接。这里,缓冲转换模块11的两种方案也可以合并为一种,电路主线路由输入耦合电路及差分放大电路组成,并通过继电器选择是否将电流-电压转换电路接入电路中,从而可以根据输入信号是电流信号或电压信号来切换继电器,在输入信号是电流信号时将电流信号转换为电压信号。

放大模块13可以由运算放大器或程控增益的可编程运算放大器构成,用于对输入信号提供程控电压增益,因为输入信号的幅值通常比较小,为了使输入信号有足够大的幅值,采用放大模块13对其进行信号放大。另外,如果输入信号较大,可以将放大模块13替换为一数控的衰减器。

滤波模块12包括50Hz/100Hz陷波器和自跟踪窄带滤波器,缓冲转换模块11依次通过50Hz/100Hz陷波器、自跟踪窄带滤波器和放大模块13连接。50Hz/100Hz陷波器的主要作用是滤除工频信号及其二次谐波的干扰,其接入与否可通过继电器分别控制,自跟踪窄带滤波器主要用于滤除输入信号中某个频率上或一定频率范围内存在的、强度较大的干扰信号,用以提高系统动态储备和减小测量误差,其接入与否也可通过继电器控制。在典型情况下,本滤波模块12可以提供不少于40db的噪声衰减,可提高本锁相放大器的动态储备、减小测量误差。

第一模拟低通滤波器41及第二模拟低通滤波器42的主要作用是对模拟信号低通滤波,限制为模拟信号的输出信号中的最高频率,通常将信号的最高频率限制在采样频率的一半以下。

第一数字低通滤波器61和第二数字低通滤波器62对模数转换后的数字输出信号进行低通滤波,相当于对输出信号进行第二级低通滤波。这里第一模拟低通滤波器41和第一数字低通滤波器61组成级联滤波器,第二模拟低通滤波器42和第二数字低通滤波器62也组成级联滤波器,起到一定程度的抗混叠滤波作用。

传统进行抗混叠滤波是采用一种宽带低通滤波器,其作用是滤除不需要的信号,并在不失真前提下,将需要数字化的信号的最高频率限制在采样频率的一半以下,避免数字信号中出现虚假信号。图5显示的是在存在较大干扰时,模拟锁相放大器进行乘法运算前后的信号变化示意图,由图中可知,由于受限于模拟低通滤波器较低的阶数和衰减特性,通常无法完全滤除干扰信号,造成信噪比降低。而本发明的锁相放大器中将前级的模拟低通滤波器和后级的数字低通滤波器组成模拟和数字混合的级联滤波器,使模拟低通滤波器并不需要完全的去除干扰信号,允许混叠信号在通带内的存在,如图6所示,依靠后级的数字低通滤波器实现高阶低通滤波并滤除干扰信号和混叠信号,本锁相放大器有效地提高了信噪比。图5和图6中,Fn表示干扰信号的频率,Fr表示参考信号的频率,Fs表示模数转换器的采样率。

优选的,第一模数转换器51和第二模数转换器52的采样速率约为100kHz,数据转换的分辨率为32位。

第一模拟低通滤波器41及第二模拟低通滤波器42采用由运算放大器构成的二阶有源低通滤波器,其带宽为30-50kHz。第一数字低通滤波器61及第二数字低通滤波器62可采用线性相位的高阶数字FIR滤波器(例如-120dB/十倍频)或高阶IIR滤波器。可以通过现场可编程逻辑阵列FPGA、单片计算机、数字信号处理器DSP甚至通用计算机等来分别或同时实现第一数字低通滤波器61、第二数字低通滤波器62及数字运算器7的功能。

幅值计算模块71、相位计算模块72分别用于计算出输入信号的幅度和相位,误差校正模块73通过对锁相放大器中的模拟乘法器、模拟低通滤波器等模拟器件由于非线性和温漂所带来的误差进行补偿或校正,反馈模块74实时将获得的输入信号中待测信号的相位返回到参考信号产生系统200的相位累加模块21,从而实现对参考信号的相位的调整。

对于相位分辨率要求较高的场合,参考信号产生系统200可以直接采用带有相位累加器的直接数字信号发生器DDS来产生参考信号,结合反馈模块74实时返回的待测信号的相位(分辨率极高的待测信号相位测量值,也可以是任意与相位有关的参数),参考信号产生系统200可以产生相位精度较高的参考信号。例如采用32位的相位累加器,可以实现至少0.001度的相位精度。

本锁相放大器在一般应用环境下,输入信号的幅值范围为1nV-1V,频率为2kHz-50MHz。

实施例二

实施例一的一种模拟数字混合结构的锁相放大器的锁相放大方法,包括:

S01、将输入信号进行缓冲,若输入信号是电流信号,则同时将其转换为电压信号;

S02、将缓冲后的输入信号依次进行滤波及信号放大。

S1、通过参考信号产生系统产生两路相互正交的正弦波信号,然后将两路相互正交的正弦波信号分别与输入信号相乘后,得到两路模拟电压输出信号。

假设输入信号的方程为:

其中,Si(t)表示输入信号, 表示输入信号中的待测信号,Ai、ω、 分别是待测信号的幅度、角频率和相位;Bi(t)是输入信号中的噪声部分。

假设参考信号产生系统产生的两路相互正交的正弦波信号为:

两路相互正交的正弦波信号作为参考信号,其角频率与待测信号的相同,均为ω,上式中Ar表示参考信号的幅度。

通过模拟乘法器将两路相互正交的正弦波信号分别与输入信号相乘,得到两路模拟电压输出信号如下:

S2、分别将该两路模拟电压输出信号进行模拟低通滤波后,进行模数转换,得到两路数字电压输出信号。

S3、分别对两路数字电压输出信号进行数字低通滤波,并滤除高频干扰信号和混叠信号后,将两路滤波后的输出信号发送到数字运算器。

步骤S2输出的两路模拟电压输出信号经过模拟低通滤波、模数转换及数字低通滤波,模拟低通滤波与数字低通滤波构成级联滤波过程,并起到一定程度的抗混叠滤波作用。数字低通滤波对两路数字电压输出信号进行第二次滤波,滤去信号中频率为ω、2ω的信号,并滤除高频干扰信号和混叠信号,滤波后的输出信号用X和Y表示,其与待测信号及参考信号的关系为:

根据上述公式,数字运算器可以根据接收到的两路滤波后的输出信号计算获得待测信号的相关参数。

S4、数字运算器接收该两路滤波后的输出信号后,计算获得输入信号中待测信号的幅值及相位,并校正由模拟运算所带来的误差,同时将获得的待测信号的相位反馈到参考信号产生系统。

这里,将获得的待测信号的相位反馈到参考信号产生系统,也可以是将获得的其它与待测信号的相位有关的参数反馈到参考信号产生系统,将反馈的相位替换为其它与相位有关的参数属于本锁相放大方法的等同替换手段,是落在本发明的保护范围内的。同样的,本发明的锁相放大器的反馈模块74反馈到参考信号产生系统200的相位也可以替换为任意与相位有关的参数。

数字运算器接收该两路滤波后的输出信号,根据步骤S3中的公式进行推断计算获得输入信号中待测信号的幅值和相位为:

在说明书附图4中,输出信号C、D两端代表的输出一般表示待测信号的幅值Ai和相位 也可以是输入到数字运算器7的两路滤波后的输出信号X和Y。A、B表示输入信号的两个输入端。

因为乘法运算以及模拟低通滤波都是模拟运算,是采用模拟乘法器和模拟低通滤波器进行运算的,由于模拟器件的非线性和温漂可能引起系统误差,所以这里要进行校正。

将获得的待测信号的相位反馈到参考信号产生系统,参考信号产生系统根据待测信号的相位调整参考信号的相位,优选的可以将参考信号的相位调整到与待测信号相位相同,此时,参考信号产生系统产生的两路相互正交的正弦波信号可表示为:

则此时,经过一系列运算后,数字低通滤波后的两路输出信号为:

由此可见,只要及时将待测信号的相位反馈到参考信号产生系统,使得其产生的两路相互正交的正弦波信号的相位与待测信号相位相同,则数字运算器就不需要通过公式计算待测信号的相位,因此可以大大减少数字运算器的运算量,实际即减少图4中幅值计算模块71和相位计算模块72的运算量,因而降低了对数字运算器的硬件要求,大大降低了本锁相放大器的生产成本。

实施例三

将实施例一的锁相放大器应用到多频率的原子力显微镜(AFM)的信号采集中,因为多频率AFM在使用中,激发了AFM微悬臂探针的多个频率的本征机械振动,需要同时检测这些频率上信号的幅度和相位。AFM微悬臂探针常用的各次本征机械振动的频率通常在10kHz至10MHz范围。对于其中某个频率信号的检测来说,其它频率的信号属于干扰信号,而且各个频率相距较近例如6倍左右,对锁相检测技术来说这是不利于精度提高的。在模拟锁相方式中,模拟滤波器的频率特性难以将相邻频率信号滤除。采用本发明的模拟数字混合结构的锁相放大器,通过模拟低通滤波器和数字低通滤波器混合的级联滤波器和自跟踪窄带滤波器可以很好的提高信噪比,提高精度。在实际的应用例中,采用以运算放大器为核心来实现模拟乘法器等模拟器件,并采用以数字信号处理器为核心来实现数字运算器等数字器件,同时开发相关的算法,可实现对原子力显微镜中各频率信号的高精度检测。

以上是对本发明的较佳实施进行了具体说明,但本发明创造并不限于实施例,熟悉本领域的技术人员在不违背本发明精神的前提下还可做出种种的等同变形或替换,这些等同的变型或替换均包含在本申请权利要求所限定的范围内。

一种模拟数字混合结构的锁相放大器及其锁相放大方法专利购买费用说明

![]()

Q:办理专利转让的流程及所需资料

A:专利权人变更需要办理著录项目变更手续,有代理机构的,变更手续应当由代理机构办理。

1:专利变更应当使用专利局统一制作的“著录项目变更申报书”提出。

2:按规定缴纳著录项目变更手续费。

3:同时提交相关证明文件原件。

4:专利权转移的,变更后的专利权人委托新专利代理机构的,应当提交变更后的全体专利申请人签字或者盖章的委托书。

Q:专利著录项目变更费用如何缴交

A:(1)直接到国家知识产权局受理大厅收费窗口缴纳,(2)通过代办处缴纳,(3)通过邮局或者银行汇款,更多缴纳方式

Q:专利转让变更,多久能出结果

A:著录项目变更请求书递交后,一般1-2个月左右就会收到通知,国家知识产权局会下达《转让手续合格通知书》。

动态评分

0.0