专利摘要

本实用新型公开了一种推挽式快速响应LDO电路,包括:第一控制电路、第二控制电路、第三控制电路、反馈电路、负载电路、误差放大器EA、功率管MP;本实用新型创造的电路结构相对于现有的LDO电路,在低功耗、大负载电流、高电源抑制比、瞬态响应等各个参数指标中均具有良好的表现,特别在瞬态响应方面表现突出,满足未来LDO电路的发展需要。该电路结构可广泛应用于SoC芯片。

权利要求

1.一种推挽式快速响应LDO电路,其特征在于,包括:第一控制电路、第二控制电路、第三控制电路、反馈电路、负载电路、误差放大器EA、功率管MP;

所述第一控制电路由:PMOS管M1、M3、NMOS管M2,电容C1、电阻R1组成,所述M1的漏极分别与所述M2的漏极、所述M3的栅极、电容C1的一端连接,所述电容C1的另一端与所述电阻R1的一端连接,所述M1的栅极与所述误差放大器EA的输出端连接,所述M1的源极、所述M3的源极分别与电源VDD连接,所述M2的源极与地GND连接,所述M3的漏极分别与所述电阻R1的另一端、所述功率管MP的栅极连接,所述M1、M3的衬底分别与所述电源VDD连接,所述M2的衬底与所述地GND连接;

所述第二控制电路由:PMOS管M4、NMOS管M5、M6组成,所述M4的漏极分别与所述M5的漏极、栅极连接,所述M4的栅极与所述误差放大器EA的输出端连接,所述M4的源极与所述电源VDD连接,所述M5的栅极与所述M6的栅极连接,所述M6的漏极与所述MP的栅极连接,所述M5、M6的源极分别与地GND连接,所述M4的衬底与电源VDD连接,所述M5、M6的衬底分别与地GND连接;

所述第三控制电路由:PMOS管M7、NMOS管M8、M9、运算放大器AMP组成,所述AMP的反相输入端分别与所述M4的栅极、所述误差放大器EA的输出端连接,所述AMP的输出端与所述M7的栅极连接,所述M7的源极与电源VDD连接,所述M7的漏极与所述M9的栅极、M8的漏极连接,所述M9的漏极与所述MP的漏极连接,所述M8、M9的源极与地GND连接,所述M7的衬底与所述电源VDD连接,所述M8、M9的衬底与地GND连接;

所述反馈电路由:NMOS管M10、M11组成,所述M10的漏极、栅极、所述M11的栅极连接所述推挽式快速响应LDO电路的输出电压端,所述输出电压端与所述MP的漏极连接,所述M10的源极分别与所述M11的漏极、所述误差放大器EA的同相输入端连接,所述M11的源极连接地GND,所述M10、M11的衬底与地GND连接;

所述负载电路由:负载电阻RL、负载电容CL组成,所述负载电阻RL与所述负载电容CL并接,所述负载电阻RL、负载电容CL的一端连接所述输出电压端连接,另一端对地GND连接;

所述误差放大器EA的反相输入端连接参考电压Vref。

2.根据权利要求1所述的一种推挽式快速响应LDO电路,其特征在于:所述功率管MP为PMOS管。

3.根据权利要求1或2所述的一种推挽式快速响应LDO电路,其特征在于:所述参考电压Vref为带隙基准电路的输出电压。

说明书

技术领域

本实用新型涉及一种调节电变量或磁变量的系统,特别涉及一种LDO(LowDropout Regulator,LDO,低压差线性稳压器)电路。

背景技术

几乎所有的电子电路都需要一个稳定的电压源,它维持在特定容差范围内,以确保正确运行(典型的CPU电路只允许电压源与额定电压的最大偏离不超过±3%)。该固定电压由某些种类的稳压器提供。LDO电路就是其中的一种稳压器。

如图1所示,典型的LDO电路包括:基准电压Vref、误差放大器EA、功率管a1、电阻分压器a2、电流源a3。该LDO电路通过电阻分压器a2自动检测输出电压Vout,误差放大器EA不断调整电流源a3从而维持输出电压Vout稳定在额定电压上。该结构的LDO电路存在负载瞬态响应能力不高的问题。然而随着集成电路的不断发展,传统的LDO结构已经不能满足低功耗、大负载电流、高电源抑制比、良好的瞬态响应等要求,因此亟需设计出新型电路。

实用新型内容

本实用新型的目的是提供一种可快速应对负载变化、具有良好瞬态响应的LDO电路。

本实用新型解决其技术问题的解决方案是:一种推挽式快速响应LDO电路,包括:第一控制电路、第二控制电路、第三控制电路、反馈电路、负载电路、误差放大器EA、功率管MP;所述第一控制电路由:PMOS管M1、M3、NMOS管M2,电容C1、电阻R1组成,所述M1的漏极分别与所述M2的漏极、所述M3的栅极、电容C1的一端连接,所述电容C1的另一端与所述电阻R1的一端连接,所述M1的栅极与所述误差放大器EA的输出端连接,所述M1的源极、所述M3的源极分别与电源VDD连接,所述M2的源极与地GND连接,所述M3的漏极分别与所述电阻R1的另一端、所述功率管MP的栅极连接,所述M1、M3的衬底分别与所述电源VDD连接,所述M2的衬底与所述地GND连接;所述第二控制电路由:PMOS管M4、NMOS管M5、M6组成,所述M4的漏极分别与所述M5的漏极、栅极连接,所述M4的栅极与所述误差放大器EA的输出端连接,所述M4的源极与所述电源VDD连接,所述M5的栅极与所述M6的栅极连接,所述M6的漏极与所述MP的栅极连接,所述M5、M6的源极分别与地GND连接,所述M4的衬底与电源VDD连接,所述M5、M6的衬底分别与地GND连接;所述第三控制电路由:PMOS管M7、NMOS管M8、M9、运算放大器AMP组成,所述AMP的反相输入端分别与所述M4的栅极、所述误差放大器EA的输出端连接,所述AMP的输出端与所述M7的栅极连接,所述M7的源极与电源VDD连接,所述M7的漏极与所述M9的栅极、M8的漏极连接,所述M9的漏极与所述MP的漏极连接,所述M8、M9的源极与地GND连接,所述M7的衬底与所述电源VDD连接,所述M8、M9的衬底与地GND连接;所述反馈电路由:NMOS管M10、M11组成,所述M10的漏极、栅极、所述M11的栅极连接所述推挽式快速响应LDO电路的输出电压端,所述输出电压端与所述MP的漏极连接,所述M10的源极分别与所述M11的漏极、所述误差放大器EA的同相输入端连接,所述M11的源极连接地GND,所述M11的衬底与地GND连接;所述负载电路由:负载电阻RL、负载电容CL组成,所述负载电阻RL与所述负载电容CL并接,所述负载电阻RL、负载电容CL的一端连接所述输出电压端连接,另一端对地GND连接;所述误差放大器EA的反相输入端连接参考电压Vref。

进一步,所述功率管MP为PMOS管。

进一步,所述参考电压Vref为带隙基准电路的输出电压。

本实用新型的有益效果是:本发明创造的电路结构相对于现有的LDO电路,在低功耗、大负载电流、高电源抑制比、瞬态响应等各个参数指标中均具有良好的表现,特别在瞬态响应方面表现突出,满足未来LDO电路的发展需要。该电路结构可广泛应用于SoC芯片。

附图说明

为了更清楚地说明本实用新型实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单说明。显然,所描述的附图只是本实用新型的一部分实施例,而不是全部实施例,本领域的技术人员在不付出创造性劳动的前提下,还可以根据这些附图获得其他设计方案和附图。

图1是背景技术中的LDO电路的结构示意图;

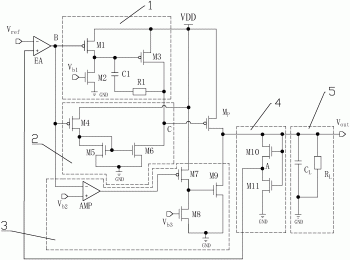

图2是本发明创造的LDO电路的结构示意图;

图3是当负载电压Vout升高时控制环路的变化情况;

图4是当负载电压Vout降低时控制环路的变化情况。

具体实施方式

以下将结合实施例和附图对本实用新型的构思、具体结构及产生的技术效果进行清楚、完整地描述,以充分地理解本实用新型的目的、特征和效果。显然,所描述的实施例只是本实用新型的一部分实施例,而不是全部实施例,基于本实用新型的实施例,本领域的技术人员在不付出创造性劳动的前提下所获得的其他实施例,均属于本实用新型保护的范围。另外,文中所提到的所有联接/连接关系,并非单指构件直接相接,而是指可根据具体实施情况,通过添加或减少联接辅件,来组成更优的联接结构。本发明创造中的各个技术特征,在不互相矛盾冲突的前提下可以交互组合。

实施例1,参考图2,一种推挽式快速响应LDO电路,包括:第一控制电路1、第二控制电路2、第三控制电路3、反馈电路4、负载电路5、误差放大器EA、功率管MP;所述功率管MP为PMOS管,所述第一控制电路1由:PMOS管M1、M3、NMOS管M2,电容C1、电阻R1组成,所述M1的漏极分别与所述M2的漏极、所述M3的栅极、电容C1的一端连接,所述电容C1的另一端与所述电阻R1的一端连接,所述M1的栅极与所述误差放大器EA的输出端连接,所述M1的源极、所述M3的源极分别与电源VDD连接,所述M2的源极与地GND连接,所述M2的栅极连接参考电压Vb1,所述M3的漏极分别与所述电阻R1的另一端、所述功率管MP的栅极连接,所述M1、M3的衬底分别与所述电源VDD连接,所述M2的衬底与所述地GND连接;所述第二控制电路2由:PMOS管M4、NMOS管M5、M6组成,所述M4的漏极分别与所述M5的漏极、栅极连接,所述M4的栅极与所述误差放大器EA的输出端连接,所述M4的源极与所述电源VDD连接,所述M5的栅极与所述M6的栅极连接,所述M6的漏极与所述MP的栅极连接,所述M5、M6的源极分别与地GND连接,所述M4的衬底与电源VDD连接,所述M5、M6的衬底分别与地GND连接;所述第三控制电路3由:PMOS管M7、NMOS管M8、M9、运算放大器AMP组成,所述AMP的反相输入端分别与所述M4的栅极、所述误差放大器EA的输出端连接,所述AMP的同向输入端与参考电压Vb2连接,所述AMP的输出端与所述M7的栅极连接,所述M7的源极与电源VDD连接,所述M7的漏极与所述M9的栅极、M8的漏极连接,所述M9的漏极与所述MP的漏极连接,所述M8的栅极连接参考电压Vb3,所述M8、M9的源极与地GND连接,所述M7的衬底与所述电源VDD连接,所述M8、M9的衬底与地GND连接;所述反馈电路4由:NMOS管M10、M11组成,所述M10的漏极、栅极、所述M11的栅极连接所述推挽式快速响应LDO电路的输出电压端,所述输出电压端与所述MP的漏极连接,所述M10的源极分别与所述M11的漏极、所述误差放大器EA的同相输入端连接,所述M11的源极连接地GND,所述M11的衬底与地GND连接;所述负载电路5由:负载电阻RL、负载电容CL组成,所述负载电阻RL与所述负载电容CL并接,所述负载电阻RL、负载电容CL的一端连接所述输出电压端连接,另一端对地GND连接;所述误差放大器EA的反相输入端连接参考电压Vref。所述参考电压Vref为带隙基准电路的输出电压,带隙基准电路可建立一个与电源和工艺无关、具有确定温度特性的直流电压,从而为运算放大器AMP提供一个稳定的电压Vref,提高LDO电路的性能。

为了方便描述,所述M10的源极、所述M11的漏极、所述误差放大器EA的同相输入端的交汇处为点A,所述误差放大器EA的输出端、所述M1栅极、M4栅极、运算放大器AMP的反相输入端的交汇处为点B,所述功率管MP的栅极、所述M3的漏极、所述M6的漏极的交汇处为点C。本发明创造的工作原理如下:

如图3,当负载发生变化,即当输出电压Vout升高时,点A处的电压升高,点A与误差放大器EA的同相输入端连接,因此点B处的电压升高,M1的栅极电压升高,流经M1的电流减小,则M3的栅极电压降低。M3栅极电压降低,则流经M3的电流增大;当点B的电压升高,M4的栅极电压增高,则流经M5的电流减小,M6与M5组成电流镜,因此流经M6的电流也减;M3的电流增大,M6的电流减小,因此点C处的电压升高。点C处的电压升高,则流经MP的电流减小;当点B处的电压升高,因其和运算放大器AMP的反相输入端连接,因此AMP的输出端电压降低,M7的栅极电压降低,M7由原来的关闭状态变为导通,则M9的栅极电压升高,流经M9的电流增大;MP的电路减小,M9的电流增大,将输出电压Vout拉低,稳定负载电压。

如图4当输出电压Vout降低时,点A处的电压降低,则EA的输出端点B的电压降低,则M1的栅极电压降低,流经M1的电流增大,则M3的栅极电压升高。M3的栅极电压升高,流经M3的电流减小;当点B处的电压降低时,M4栅极电压降低,流经M4的电流增大,则流经M6的电流增大;流经M3的电流减小,流经M6的电流增大,则点C处的电压降低,流经MP的电流增大,将输出电压Vout拉高,稳定负载电压。当点B处的电压降低时,AMP的输出端电压为高电平,因为M7为PMOS,所以M7处于闭合状态,不工作。即第三控制电路3不工作,图4中以未画出第三控制电路3作为提示。

下面对电路进行定量分析:术语解释:I1为流经M1的电流,I2为流经M2的电流,I3为流经M3的电流,I4为流经M4的电流,I5为流经M5的电流,I6为流经M6的电流,IP为流经MP的电流,I8为流经M8的电流,I9为流经M9的电流,I10为流经M10的电流,I11为流经M11的电流;

1.反馈电路4

点A处的电压是随输出电压Vout同步变化的。由图2可知M10的连接方式为二极管连接,因此处于饱和区,M11可能处于饱和区,也可能处于线性区。

1.1假设M11处于饱和区

VGS11=Vout (3)

VGS10=Vout-VA (4)

I11=I10 (5)

其中Ki=μn,Cox(W/L)ii=1,2…

由式(1)(2)(3)(4)(5)得

对式(6)求导得

1.2当M11工作在三极管区的时候,其电流公式为

VDS11=VA (9)

由式(1)(5)可得

由式(3)(4)(8)(9)(10)可得

对式(11)求导可得

VA是A点电压,VGS是MOS管的栅源电压,VDS是CMOS晶体管的漏源电压。VTH是CMOS管的阈值电压。μn是电子的迁移率,μp是空穴的迁移率。Cox是单位面积栅电容。W是导电沟道宽度,L是导电沟道长度,(W/L)是CMOS晶体管的宽长比。

在式(7)中我们可以通过调节M10和M11宽长比,使它的值大于零,而式(12)其值大于零。因此,由式(7)和(12)可以看出,点A处的电压与输出电压之间的导数为正,因此它们之间呈正比关系。点A处的电压随输出的变化而变化。

2.控制电路部分,

2.1第一控制电路1

如图2所示,M1和M2为采用电流源负载的共源极电路。设PMOS电流由源极流向漏极,则流经PMOS管M1的电流为

VGS1=VDD-VB (14)

设点B的电压变化量为ΔVB,则由式(13)(14)可得

当点B的电压增加时ΔVB为正,减小时ΔVB为负。由式(15)可知当点B电压增加时,电流I1减小,点B电压减小时,电流I1增大。又因为M2连接偏置电压,相当于一个电流源,其电流不变,因此当I1减小时M3栅极电压降低,I1增加时M3栅极电压增大。

流经M3的电流为

VGS1=VDD-VG3 (17)

设M3的栅极电压的变化量为ΔVG3,则由式(16)(17)可得

由式(18)可知,当M3栅极电压升高时I3减小,当M3栅极电压降低时I3升高。

2.2第二控制电路2

第二控制电路2中的PMOS管M4和M5的连接方式为采用二极管连接的负载的共源级电路。其与M1和M2组成的电路只是负载不同,因此M1和M4的电流变化情况是相同的。

M4的负载M5是二极管连接方式,所以M5可以等效为一个小信号电阻。M5和M6又构成电流镜,因此M5和M6中的电流是同步变化的。

因此由对M1的分析可知,当点B电压升高时流经M4的电流I4减小,点B电压降低时流经M4的电流I4增大。由M6和M5电流变化一样,因此I4减小时I6也减小I4增大时I6也增大。

2.3功率管MP

流经MP的电流为

VGSP=VDD-VC (20)

又输出电压Vout为

Vout=Iout·Zout (21)

Iout=αIP (22)

Zout为输出阻抗。

设点C的电压变化为ΔVC,则由式(19)(20)(21)(22)可得

由式(23)可知当点C电压升高时Iout减小,ΔVC为正,输出电压Vout降低,恢复正常状态;点C电压降低时Iout增大,ΔVC为正,输出电压Vout升高,恢复正常状态,稳定负载电压。

2.4第三控制电路3

如图2所示,M7接运算放大器AMP输出端,M8接偏置电压Vb3。M7和M8组成采用电流源负载的共源级电路。I8电流公式为

由式(24)可知当VGS8较小时,I8也比较小。

正常情况下,AMP输出的电压为VDD电压,因此M7是处于截至区,因为M7是PMOS管,只有当栅源电压VGS7小于阈值电压时M7才会导通。

当点B电压升高时,通过运算放大器反相输入端,此时AMP输出电压为零,因此M7导通,第三控制电路3开始工作。此时M9栅极电压增大。

M9的电流公式为

设M7栅极电压变化为ΔVGS9,则由式(25)可得

由式(26)可知,当M9栅极电压升高时,M9中的电流增大,将输出电压Vout拉低。

由对反馈电路4、第一控制电路1、第二控制电路2分析可知,当输出电压Vout升高时,点B处的电压升高,M3中的电流I3增大,M6中的电流I6减小,因此点C处的电压被拉高。点C处的电压升高,则流经MP的电流降低。由对第三控制电路3的分析可知,点B处的电压升高,运算放大器AMP的输出端电压降低,M7的栅极电压降低,M7导通控制电路开始工作,因此M9的栅极电压被拉高,流经M9的电流增大。综上,当输出电压Vout升高时,MP中的电流减小,M9中的电流增大,将输出电压Vout拉低,恢复到正常状态,稳定负载电压。

当输出电压Vout减小时,点B处的电压降低,M3中的电流减小,M6中的电流增大,因此点C处的电压被拉低,流经MP的电流增大,输出电压Vout被拉高,恢复正常状态,稳定负载电压。

通过仿真,本发明创造的LDO电路可以在8ns以内便能使LDO电路的负载电压恢复正常状态,相对于传统LDO电路具有明显优势。

以上对本实用新型的较佳实施方式进行了具体说明,但本发明创造并不限于所述实施例,熟悉本领域的技术人员在不违背本实用新型精神的前提下还可做出种种的等同变型或替换,这些等同的变型或替换均包含在本申请权利要求所限定的范围内。

一种推挽式快速响应LDO电路专利购买费用说明

![]()

Q:办理专利转让的流程及所需资料

A:专利权人变更需要办理著录项目变更手续,有代理机构的,变更手续应当由代理机构办理。

1:专利变更应当使用专利局统一制作的“著录项目变更申报书”提出。

2:按规定缴纳著录项目变更手续费。

3:同时提交相关证明文件原件。

4:专利权转移的,变更后的专利权人委托新专利代理机构的,应当提交变更后的全体专利申请人签字或者盖章的委托书。

Q:专利著录项目变更费用如何缴交

A:(1)直接到国家知识产权局受理大厅收费窗口缴纳,(2)通过代办处缴纳,(3)通过邮局或者银行汇款,更多缴纳方式

Q:专利转让变更,多久能出结果

A:著录项目变更请求书递交后,一般1-2个月左右就会收到通知,国家知识产权局会下达《转让手续合格通知书》。

动态评分

0.0