专利摘要

本发明涉及集成电路技术领域,特别是一种基于阈值逻辑的SET/MOS混合结构的7-3计数器,包括一个七输入阈值逻辑门、一个八输入阈值逻辑门和一个九输入阈值逻辑门;该电路仅由3个阈值逻辑门和2个反相器构成,共消耗5个PMOS管,5个NMOS管和3个SET。而基于布尔逻辑的CMOS7-3计数器则要消耗194个晶体管。整个电路的平均功耗仅为6.92nW。相比而言,本发明提出的7-3计数器管子数目大大减少,电路功耗显著降低,电路结构得到了进一步的简化,有望应用于乘法器、多输入加法器以及数字信号处理器中。

说明书

技术领域

本发明涉及集成电路技术领域,特别是一种由纳米器件组成的基于阈值逻辑的SET/MOS混合结构的7-3计数器。

背景技术

7-3计数器作为基本的数字电路单元,能够计算输入信号中高电平的个数,编码为3位的二进制数。7-3计数器广泛应用于乘法器、多输入加法器以及数字信号处理器中。现有的7-3计数器主要由传统的CMOS晶体管构成。基于CMOS器件的7-3计数器电路结构复杂,需要消耗较多的晶体管,电路功耗较大,集成度不高。

发明内容

本发明的目的是提供一种基于阈值逻辑的SET/MOS混合结构的7-3计数器。

本发明采用以下方案实现:一种基于阈值逻辑的SET/MOS混合结构的7-3计数器,包括一个七输入阈值逻辑门、一个八输入阈值逻辑门和一个九输入阈值逻辑门;所述七输入阈值逻辑门的输出端经第一反相器与所述八输入阈值逻辑门的第八输入端、九输入阈值逻辑门的第八输入端连接;所述八输入阈值逻辑门的输出端经第二反相器与所述九输入阈值逻辑门的第九输入端连接;所述七、八、九输入阈值逻辑门由SET/MOS混合电路构成,其阈值为1.5,其输出逻辑是根据输入的权重值计算出总输入值,并将总输入值与所述阈值进行比较,大于或等于所述阈值,则输出为1,否则输出为0。

在本发明一实施例中,所述七、八、九输入阈值逻辑门的阈值逻辑满足逻辑方程:

其中Wi为输入Xi对应的权重,n为输入的个数, θ为阈值。

在本发明一实施例中,所述的SET/MOS混合电路包括:一PMOS管,其源极接电源端Vdd;一NMOS管,其漏极与所述PMOS管的漏极连接;以及一SET管,其与所述NMOS管的源极连接。

在本发明一实施例中,所述PMOS管M1的参数满足:沟道宽度Wp为22 nm,沟道长度Lp为154 nm,栅极电压Vpg为0.4V;所述NMOS管M2的参数满足:沟道宽度Wn为22 nm,沟道长度Ln为154 nm,栅极电压Vng为0.4 V;所述SET管的参数满足:隧穿结电容Cs, Cd为0.1 aF;隧穿结电阻Rs, Rd为600 KΩ;背栅电压Vctrl为0.762 V,背栅电容Cctrl为0.1050 aF,耦合电容C2为0.0150 aF,耦合电容C1为0.0095 aF;耦合电容C0为0.0080 aF。

本发明利用单电子晶体管与MOS管混合结构所具有的库仑阻塞振荡效应和多栅输入特性,实现了基于阈值逻辑的SET/MOS混合结构的7-3计数器。由于阈值逻辑强大的逻辑功能,该电路仅由3个阈值逻辑门和2个反相器构成, 共消耗5个PMOS管,5个NMOS管和3个SET。而基于布尔逻辑的CMOS 7-3计数器则要消耗194个晶体管。HSPICE的仿真结构表明该电路能够实现7-3计数器的功能,整个电路的平均功耗仅为19.7 nW。相比而言,本发明提出的7-3计数器管子数目大大减少,电路功耗显著降低,电路结构得到了进一步的简化,有望应用于乘法器、多输入加法器以及数字信号处理器等电路中。

附图说明

图1为阈值逻辑门示意图。

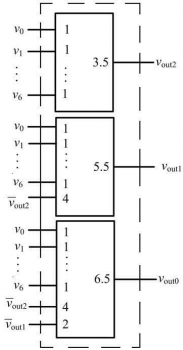

图2为SET/MOS混合结构7-3计数器原理图。

图3为多栅输入SET/MOS混合电路原理图。

图4为SET/MOS混合电路的输入输出特性曲线。

图5a和图5b为SET/MOS混合结构7-3计数器仿真特性曲线。

具体实施方式

下面结合附图及实施例对本发明做进一步说明。

如图2所示,本发明提供一种基于阈值逻辑的SETMOS混合结构的7-3计数器,包括一个七输入阈值逻辑门、一个八输入阈值逻辑门和一个九输入阈值逻辑门;所述七输入阈值逻辑门的输出端经第一反相器与所述八输入阈值逻辑门的第八输入端、九输入阈值逻辑门的第八输入端连接;所述八输入阈值逻辑门的输出端经第二反相器与所述九输入阈值逻辑门的第九输入端连接;所述七、八、九输入阈值逻辑门由SET/MOS混合电路构成,其阈值为1.5,其输出逻辑是根据输入的权重值计算出总输入值,并将总输入值与所述阈值进行比较,大于或等于所述阈值,则输出为1,否则输出为0。

具体的说,本发明采用单电子晶体管(Single electron transistor, SET)和MOS管相混合的方式进行7-3计数器的设计。单电子晶体管是新一代纳米电子器件,具有独特的库仑阻塞和库仑振荡效应。SET具有超小的器件尺寸和超低的电路功耗,在功耗、工作速度等方面相对于传统的微电子器件具有明显的优势,有望成为制造下一代低功耗、高密度超大规模集成电路理想的基本器件。同时单电子晶体管能够与CMOS硅工艺相兼容,有利于充分利用现有的CMOS技术的优势进行电路设计。这使得SET/MOS混合结构成为单电子晶体管的一个重要研究方向。SET/MOS混合电路具备SET和MOS管的优越性能,表现出极低的功耗、超小的器件尺寸、较强的驱动能力和较大的输出摆幅,在数字电路中得到了广泛的应用。

此外,SET/MOS混合电路可以不遵循传统的基于布尔逻辑的设计方法,而采用阈值逻辑来进行电路的设计。由于阈值逻辑具有比布尔逻辑复杂的逻辑过程,能够更有效地实现逻辑功能。因此基于阈值逻辑的SET/MOS混合结构的电路设计,有望增强电路的功能,提高电路的集成度。

本发明的阈值逻辑的主要原理是根据输入的权重计算出总输入值,将总输入值与阈值进行比较得出输出逻辑。若总输入值大于等于阈值,则输出为1,否则为0。阈值逻辑要满足的逻辑方程如式(1)所示,其中Wi为输入Xi对应的权重,n为输入的个数,θ为阈值。阈值逻辑门的示意图如图1所示。基于阈值逻辑的电路设计首先要确定电路的阈值逻辑表达式,关键是确定电路中各个输入的权重和电路的阈值。

(1)

本发明的7-3计数器能够计算输入信号中逻辑“1”的个数,以3位的二进制数的形式输出。请继续参照图2,该7-3计数器由3个阈值逻辑门和两个反相器构成, 7个输入为V0-V6,输出为Vout0-Vout2。该结构可以实现输入中逻辑“1”个数的计算,并输出3位二进制数。3个输出的阈值逻辑表达式如式(2)、(3)、(4)所示, 、 、 为输出, 、 为 、 经过反相器的输出值。图2中的每个阈值逻辑门均由一个多栅输入的SET/MOS混合电路构成,其原理图如图3所示。该电路由1个PMOS管,1个NMOS管和1个多栅输入的SET串联而成。电路中PMOS管作为恒流源为整个电路提供偏置电流。由于SET正常工作的电流都很小,一般为nA数量级,所以PMOS管应该工作在亚阈值区。NMOS管的栅极偏压Vng是固定的,其值略大于NMOS管的阈值电压Vth, 使SET的漏极电压固定为Vng-Vth。栅压V1,V2,……,Vn通过电容耦合到库仑岛上。耦合电容构成了一个电容的阵列,用于计算总输入值。根据阈值逻辑的定义,通过比较总输入电压与电路阈值就可以得到对应的输出逻辑。当总输入电压大于阈值时,输出为高电平(逻辑“1”);当总输入电压小于阈值时,输出为低电平(逻辑“0”)。通过设置合适的电路参数,SET/MOS混合电路对应的输入输出(Vin-Vout)特性曲线如图4所示。输出电压随着输入电压的变化而变化。当输入电压超过某个数值(即电路的阈值,如图4中的400mV)时,输出实现从低电平到高电平的跳变。通过偏置SET的背栅电压(Vctrl),可以得到不同的阈值。因此,SET/MOS混合电路能够实现阈值逻辑门的功能。

(2)

(3)

(4)

本发明利用HSPICE对基于阈值逻辑的7-3计数器进行功能的仿真验证。SET的模型是目前广泛使用、精度高的宏模型(Compact macromodel)。该模型以子电路的形式定义在SPICE中。MOS管的模型使用目前公认的22 nm的预测技术模型(Predictive technology model)。在7-3计数器的电路中,除了单位输入耦合电容(C0,C1,C2)外,3个阈值逻辑门具有相同的仿真参数,其中C0,C1,C2分别对应于产生输出Vout0,Vout1,Vout2的阈值逻辑门。在电路中,电源电压Vdd设置为0.80V,PMOS管和NMOS管的宽长比(W/L)均设为1/7,主要的电路仿真参数如表1所示。

表1

仿真得到的特性曲线如图5a和图5b所示。在图5a中,输入信号均设为方波,输入的高低电平分别为0.8 V和0 V。仿真得到的输出波形能够计算输入中逻辑“1”的个数,以3为二进制数的形式输出,如图5b所示。因此本发明提出的结构能够有效地实现7-3计数器的功能。

以上所述仅为本发明的较佳实施例,凡依本发明申请专利范围所做的均等变化与修饰,皆应属本发明的涵盖范围。

基于阈值逻辑的SET/MOS混合结构的7-3计数器专利购买费用说明

![]()

Q:办理专利转让的流程及所需资料

A:专利权人变更需要办理著录项目变更手续,有代理机构的,变更手续应当由代理机构办理。

1:专利变更应当使用专利局统一制作的“著录项目变更申报书”提出。

2:按规定缴纳著录项目变更手续费。

3:同时提交相关证明文件原件。

4:专利权转移的,变更后的专利权人委托新专利代理机构的,应当提交变更后的全体专利申请人签字或者盖章的委托书。

Q:专利著录项目变更费用如何缴交

A:(1)直接到国家知识产权局受理大厅收费窗口缴纳,(2)通过代办处缴纳,(3)通过邮局或者银行汇款,更多缴纳方式

Q:专利转让变更,多久能出结果

A:著录项目变更请求书递交后,一般1-2个月左右就会收到通知,国家知识产权局会下达《转让手续合格通知书》。

动态评分

0.0