专利摘要

本发明公开了一种高动态脉冲成形信号模拟方法和装置,其中,该装置包括:参数计算模块与成形滤波器模块;参数计算模块包括上位机、NCO累加器、存储器与参数解算模块;成形滤波器模块包括并行的多个FIR滤波器模块与加权求和模块;FIR滤波器模块又包括寻址控制子模块、参数控制子模块、滤波器系数ROM以及基本FIR滤波器。本发明采用多项式的插值滤波器实现,不仅可以实现变比率采样率转换,同时不存在中间采样率概念。而且,基于多项式的插值滤波器采用Farrow结构,大大降低了实现复杂度。因此,本发明采用基于多项式的插值滤波器可以满足高动态脉冲成形信号模拟的基本要求。

权利要求

1.一种高动态脉冲成形信号模拟装置,其特征在于,包括:参数计算模块与成形滤波器模块;参数计算模块包括上位机、NCO累加器、存储器与参数解算模块;成形滤波器模块包括并行的N+1个FIR滤波器模块与加权求和模块;FIR滤波器模块又包括寻址控制子模块、参数控制子模块、滤波器系数ROM以及基本FIR滤波器;

上位机,用于根据接收自外部的符号速率R0、符号多普勒速率Rd[k]以及运动初始距离d0,计算得到频率字FW[k]与NCO累加器初值m0、μ0,将其输出给NCO累加器;

NCO累加器,用于对接收自上位机的累加器初值m0、μ0及频率字FW[k]并进行累加,获得基本点索引mk和小数间隔μk,将基本点索引mk输出给存储器,将小数间隔μk输出给参数解算模块;其中,

其中,p为NCO累加器的量化位数,k为频率字索引;

存储器,用于根据接收的基本点索引mk读取存储的待传输信息的符号x[mk],输出给并行的FIR滤波器模块;

参数解算模块,用于根据接收到的pbit的小数间隔μk产生符号内分段索引i′k与段内小数间隔μ′k;i′k为μk的高qbit,μ′k为μk的低p-q bit;将符号内分段索引i′k输出给各FIR滤波器模块,将段内小数间隔μ′k输出给加权求和模块;

FIR滤波器模块中的寻址控制子模块,用于根据接收到的符号内分段索引i′k产生地址i″k至滤波器系数ROM:当符号内分段索引i′k最高位为‘0’时,输出i′k的低q-1bit作为地址i″k;当符号内分段索引i′k最高位为‘1’时,对i′k的低q-1bit求反作为地址i″k;

滤波器系数ROM,用于存储FIR滤波器系数矩阵C(n);C(n)中滤波器系数的获取方式为:利用窗函数对成形滤波器冲击响应截断、平滑,对加窗后的冲击响应等间隔分段,每个符号内分段个数为γ=2q,q为设定的数值;然后基于拉格朗日插值用N阶多项式对分段后的冲击响应近似,并求解滤波器系数并存储;其中,C(n)上下平均分割为两部分Cl(n)与Cr(n),根据对称性仅存储Cl(n);n为并行FIR滤波器模块的索引,n=0,1,...,N;

滤波器系数ROM根据所接收的地址i″k提取相应的滤波器系数C(n,i″k),并输出给系数控制子模块;

系数控制子模块,用于根据接收到的符号内分段索引i′k以及滤波器系数C(n,i″k),产生基本FIR滤波器所需的相应乘法器上的滤波器系数:当i′k的最高位为‘0’时,将所接收的滤波器系数C(n,i″k)直接输出至基本FIR滤波器相应位置的乘法器上;当i′k的最高位为‘1’时,将所接收的滤波器系数C(n,i″k)乘以(-1)n后输出至基本FIR滤波器相反位置的乘法器上;

基本FIR滤波器,用于根据接收到的符号x[mk]以及滤波器系数,经过滤波运算输出结果v(n)至加权求和模块;

加权求和模块,用于根据接收到输出结果v(n),经过加权求和运算,得到最终的离散高动态脉冲成形信号yd[k]:

2.一种高动态脉冲成形信号模拟方法,其特征在于,

步骤一、利用窗函数对成形滤波器冲击响应截断、平滑,对加窗后的冲击响应等间隔分段,每个符号内分段个数为γ=2q,q为设定的数值;然后基于拉格朗日插值用N阶多项式对分段后的冲击响应近似,并求解滤波器系数矩阵C(n),并存储到并行FIR滤波器中的滤波器系数ROM中;

步骤二、NCO累加器量化位数为p,根据 获得频率字FW[k],根据 对频率字FW[k]进行累加,计算得到基本点索引mk,并利用 计算得到小数间隔μk;

其中,R0=1/T0为已知的符号速率,Rd[k]为符号多普勒速率,fs为模拟频率;m0、μ0均为累加初值;

步骤三、根据基本点索引mk,读取存储的待传输信息的符号x[mk],输出给成形滤波器模块;根据pbit的小数间隔μk产生符号内分段索引i′k与段内小数间隔μ′k;i′k为μk的高qbit,μ′k为μk的低p-qbit;将符号内分段索引i′k和段内小数间隔μ′k输出给成形滤波器模块;成形滤波器模块中包括N+1个并行的FIR滤波器,每个FIR滤波器中具有基本FIR滤波器和滤波器系数ROM;

步骤四、成形滤波器模块接收存储器输出的符号x[mk],并保存在基本FIR滤波器中的移位寄存器中;

步骤五、成形滤波器模块中的并行的FIR滤波器接收符号内分段索引i′k,其最高位MSB作为控制位,低q-1位用于产生滤波器系数ROM的地址;当最高位MSB为‘0’时,将i′k的低q-1位作为地址i″k;当最高位MSB为1时,对i′k的低q-1bit逐位取反,再作为地址i″k;

步骤六、各FIR滤波器中滤波器系数ROM存储有步骤一得到的基本FIR滤波器的滤波器系数矩阵C(n),且C(n)上下平均分割为两部分Cl(n)与Cr(n),根据对称性仅存储Cl(n);n为并行FIR滤波器的索引,n=0,1,...,N;根据步骤五产生的地址i″k,对滤波器系数ROM寻址,提取滤波器系数C(n,i″k);当所述符号内分段索引i′k的最高位MSB为‘0’时,直接输出滤波器系数C(n,i″k)至基本FIR滤波器相应位置的乘法器上;当所述符号内分段索引i′k的最高位MSB为‘1’时,将提取的滤波器系数C(n,i″k)乘以(-1)n后输出至相反位置的基本FIR滤波器的乘法器上;

步骤七、基本FIR滤波器接收符号x[mk]及滤波器系数C(n,i″k),进行滤波操作,输出滤波结果v(n);

步骤八、并行FIR滤波器的滤波结果v(n)再与参数μk进行加权求和处理,最终输出高动态脉冲成形信号:

说明书

技术领域

本发明属于航天测控通信、卫星导航定位、卫星通信领域,尤其涉及一种高动态脉冲成形信号模拟方法和装置。

背景技术

脉冲成形滤波作为数字通信的基本技术,可以有效提高频谱利用率,降低码间串扰,并广泛应用于各种通信领域,包括航天测控通信及卫星通信领域。无论是航天测控通信还是卫星通信领域,它们均工作在高动态环境下,为了测试和验证系统对多普勒效应的处理能力,需要信号模拟器对脉冲成形信号的高动态特性进行模拟。

脉冲成形滤波器是一种常规的脉冲成形信号产生设备,针对不同的应用背景或目的,脉冲成形滤波器结构也不尽相同,主要包括FIR、IIR、递归结构等。这一类方法的主要问题在于只能实现固定比率的采样率转换,从而无法实现高动态脉冲成形信号的模拟。

为了高动态脉冲成形信号的模拟,需要实现变比率的采样率转换,目前国内外主要的研究包括查表法,脉冲成形滤波器与CIC滤波器级联、基于多抽样率的多项结构滤波器组实现、基于多项式的插值滤波器实现等。第一类方法的主要问题在于需要较大的存储器存储脉冲成形滤波器的离散冲击响应序列,因此占用过多硬件资源;第二、三类方法的主要问题在于对于某些采样率转换比率需要很高的中间采样率,致使脉冲成形滤波器难以实现;第四类方法的主要问题在于滤波器性能通常会受到多项式对滤波器冲击响应近似程度的影响。

针对上述问题,本发明提出了一种高动态脉冲成形信号模拟方法,采用基于多项式的插值滤波器实现;并对传统的基于多项式的插值滤波器设计及结构进行改进,使其具备更好频域性能,国内外未见相关报道。

发明内容

有鉴于此,本发明提供了一种高动态脉冲成形信号模拟方法和装置,解决基于多项式的插值滤波器实现模拟时,滤波器性能通常会受到多项式对滤波器冲击响应近似程度的影响的问题,可以得到较好的频域性能。

为了解决上述技术问题,本发明是这样实现的:

一种高动态脉冲成形信号模拟装置,包括:参数计算模块与成形滤波器模块;参数计算模块包括上位机、NCO累加器、存储器与参数解算模块;成形滤波器模块包括并行的N+1个FIR滤波器模块与加权求和模块;FIR滤波器模块又包括寻址控制子模块、参数控制子模块、滤波器系数ROM以及基本FIR滤波器;

上位机,用于根据接收自外部的符号速率R0、符号多普勒速率Rd[k]以及运动初始距离d0,计算得到频率字FW[k]与NCO累加器初值m0、μ0,将其输出给NCO累加器;

NCO累加器,用于对接收自上位机的累加器初值m0、μ0及频率字FW[k]并进行累加,获得基本点索引mk和小数间隔μk,将基本点索引mk输出给存储器,将小数间隔μk输出给参数解算模块;其中,

其中,p为NCO累加器的量化位数,k为频率字索引;

存储器,用于根据接收的基本点索引mk读取存储的待传输信息的符号x[mk],输出给并行的FIR滤波器模块;

参数解算模块,用于根据接收到的pbit的小数间隔μk产生符号内分段索引ik′与段内小数间隔μk′;ik′为μk的高qbit,μk′为μk的低p-q bit;将符号内分段索引ik′输出给各FIR滤波器模块,将段内小数间隔μk′输出给加权求和模块;

FIR滤波器模块中的寻址控制子模块,用于根据接收到的符号内分段索引ik′产生地址ik″至滤波器系数ROM:当符号内分段索引ik′最高位为‘0’时,输出ik′的低q-1bit作为地址ik″;当符号内分段索引ik′最高位为‘1’时,对ik′的低q-1bit求反作为地址ik″;

滤波器系数ROM,用于存储FIR滤波器系数矩阵C(n);C(n)中滤波器系数的获取方式为:利用窗函数对成形滤波器冲击响应截断、平滑,对加窗后的冲击响应等间隔分段,每个符号内分段个数为γ=2q,q为设定的数值;然后基于拉格朗日插值用N阶多项式对分段后的冲击响应近似,并求解滤波器系数并存储;其中,C(n)上下平均分割为两部分Cl(n)与Cr(n),根据对称性仅存储Cl(n);n为并行FIR滤波器模块的索引,n=0,1,...,N;

滤波器系数ROM根据所接收的地址ik″提取相应的滤波器系数C(n,ik″),并输出给系数控制子模块;

系数控制子模块,用于根据接收到的符号内分段索引ik′以及滤波器系数C(n,ik″),产生基本FIR滤波器所需的相应乘法器上的滤波器系数:当ik′的最高位为‘0’时,将所接收的滤波器系数C(n,ik″)直接输出至基本FIR滤波器相应位置的乘法器上;当ik′的最高位为‘1’时,将所接收的滤波器系数C(n,ik″)乘以(-1)n后输出至基本FIR滤波器相反位置的乘法器上;

基本FIR滤波器,用于根据接收到的符号x[mk]以及滤波器系数,经过滤波运算输出结果v(n)至加权求和模块;

加权求和模块,用于根据接收到输出结果v(n),经过加权求和运算,得到最终的离散高动态脉冲成形信号yd[k]:

一种高动态脉冲成形信号模拟方法,包括如下步骤:

步骤一、利用窗函数对成形滤波器冲击响应截断、平滑,对加窗后的冲击响应等间隔分段,每个符号内分段个数为γ=2q,q为设定的数值;然后基于拉格朗日插值用N阶多项式对分段后的冲击响应近似,并求解滤波器系数矩阵C(n),并存储到并行FIR滤波器中的滤波器系数ROM中;

步骤二、NCO累加器量化位数为p,根据 获得频率字FW[k],根据 对频率字FW[k]进行累加,计算得到基本点索引mk,并利用 计算得到小数间隔μk;

其中,R0=1/T0为已知的符号速率,Rd[k]为符号多普勒速率,fs为模拟频率;m0、μ0均为累加初值;

步骤三、根据基本点索引mk,读取存储的待传输信息的符号x[mk],输出给成形滤波器模块;根据pbit的小数间隔μk产生符号内分段索引ik′与段内小数间隔μk′;ik′为μk的高qbit,μk′为μk的低p-qbit;将符号内分段索引ik′和段内小数间隔μk′输出给成形滤波器模块;成形滤波器模块中包括N+1个并行的FIR滤波器,每个FIR滤波器中具有基本FIR滤波器和滤波器系数ROM;

步骤四、成形滤波器模块接收存储器输出的符号x[mk],并保存在基本FIR滤波器中的移位寄存器中;

步骤五、成形滤波器模块中的并行的FIR滤波器接收符号内分段索引ik′,其最高位MSB作为控制位,低q-1位用于产生滤波器系数ROM的地址;当最高位MSB为‘0’时,将ik′的低q-1位作为地址ik″;当最高位MSB为1时,对ik′的低q-1bit逐位取反,再作为地址ik″;

步骤六、各FIR滤波器中滤波器系数ROM存储有步骤一得到的基本FIR滤波器的滤波器系数矩阵C(n),且C(n)上下平均分割为两部分Cl(n)与Cr(n),根据对称性仅存储Cl(n);n为并行FIR滤波器的索引,n=0,1,...,N;根据步骤五产生的地址ik″,对滤波器系数ROM寻址,提取滤波器系数C(n,ik″);当所述符号内分段索引ik′的最高位MSB为‘0’时,直接输出滤波器系数C(n,ik″)至基本FIR滤波器相应位置的乘法器上;当所述符号内分段索引ik′的最高位MSB为‘1’时,将提取的滤波器系数C(n,ik″)乘以(-1)n后输出至相反位置的基本FIR滤波器的乘法器上;

步骤七、基本FIR滤波器接收符号x[mk]及滤波器系数C(n,ik″),进行滤波操作,输出滤波结果v(n);

步骤八、并行FIR滤波器的滤波结果v(n)再与参数μk进行加权求和处理,最终输出高动态脉冲成形信号:

有益效果:

1、本设计可以有效实现高动态脉冲成形信号模拟,并适用于任意基带波形。

2、与众多脉冲成形滤波器实现方法相比,基于多项式的插值滤波器不仅可以实现变比率采样率转换,同时不存在中间采样率概念。基于多项式的插值滤波器可以满足高动态脉冲成形信号模拟的基本要求,从而本发明采用该滤波器实现。

3、基于多项式的插值滤波器采用Farrow结构,大大降低了实现复杂度。

4、引入新的脉冲成形滤波器设计参数γ,可以有效改善脉冲成形滤波器的频域性能,使得通带足够平坦,阻带抑制足够大;从而有效改善高动态脉冲成形信号的旁瓣抑制;同时,还可以在滤波器性能及实现复杂度等方面进行调节,使设计更为灵活;与其他方法相比,在滤波器性能相同的情况下,可以有效降低滤波器乘法器数量。

附图说明

图1为高动态脉冲成形信号模数混合模型。

图2为简化后的离散高动态脉冲成形信号模型。

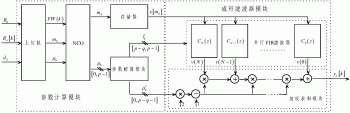

图3为高动态脉冲成形信号模拟方法框图。

图4为索引为n的FIR滤波器结构框图。

具体实施方式

下面结合附图并举实施例,对本发明进行详细描述。

针对高动态脉冲成形信号模拟问题,需要采样率转换比率可以实时变化,同时希望尽量降低实现复杂度。与众多脉冲成形滤波器实现方法相比,基于多项式的插值滤波器不仅可以实现变比率采样率转换,同时不存在中间采样率概念;而且,基于多项式的插值滤波器采用Farrow结构,大大降低了实现复杂度。因此,基于多项式的插值滤波器可以满足高动态脉冲成形信号模拟的基本要求,从而本发明采用该滤波器实现。然而,为了解决滤波器性能受到多项式对冲击响应近似程度影响的问题,本发明还对该滤波器设计方法与结构进行改进,同样可以得到较好的频域性能。

本发明提供了一种高动态脉冲成形信号模拟装置,其包括:参数计算模块以及成形滤波器模块。其中成形滤波器模块的设计是本发明的核心。下面简述高动态脉冲成形信号模拟方法原理以及成形滤波器设计步骤。

根据基带脉冲成形信号在动态信道内传输特点,建立高动态脉冲成形信号模数混合模型,从而对离散高动态脉冲成形信号建模。高动态脉冲成形信号模数混合模型主要由四部分组成,如图1所示,包括数字/脉冲序列转换,脉冲成形滤波器、动态信道模型以及信号采样。

数字/脉冲序列转换部分将离散时间的待传输的基带符号序列表示为连续时间的符号脉冲序列,即

其中x[l]为基带符号序列,T0为符号位宽,δ(t)为单位冲击函数,t为时间变量。连续时间符号脉冲序列经过脉冲成形滤波器可得连续时间的无动态脉冲成形信号

其中hPSF(t)为脉冲成形滤波器的冲击响应。

动态信道模型用于模拟动态信道的传输时延特性,其频率响应可以表示为

HC(jΩ)=e-jΩD,(C3)

其中Ω为模拟域频率,D为传输时延。因此,高动态脉冲成形信号为

最后,对上述连续高动态脉冲成形信号采样,采样时刻为t=kTs,Ts为模拟时钟周期,从而得到离散高动态脉冲成形信号模型为:

根据插值理论,定义基本点索引mk与小数间隔μk为

其中 为向下取整操作。再对脉冲成形滤波器冲击响应加窗截断,即

h(t)=hPSF(t)w(t),(C7)

其中w(t)为窗函数,截断长度为2IT0,截断范围t∈[-IT0,IT0)。因此,(C5)可以重写为

其中i=mk-l。所以,高动态脉冲成形信号模数混合模型可以简化为一个单独的数字脉冲成形滤波器,如图2所示,其离散时间的冲击响应为h(i,μk)=h[(i+μk)T0],输入为基带符号序列x[mk],输出即为离散高动态脉冲成形信号yd[k]。

由于模拟的高动态特性主要体现在传输延时D中,且由(C6)可知传输延时D影响了基本点索引mk与小数间隔μk的取值。因此,高动态特性完全由参数mk及μk决定。下面对参数mk、μk与动态多普勒频率的关系进行分析。

假设信号接收机在t时刻接收到信号的传输距离为d(t),则相应传输延时为

其中c为光速。假设信号发射机静止,接收机的径向运动速度为v(t),则信号传输距离d(t)可以表达为

其中d0为t=0时刻信号的传输距离。根据多普勒效应,符号多普勒速度定义为:

其中R0=1/T0为符号速率。将(C10)代入(C9)可得

对上式采样可得

其中Rd[l]=Rd(lTs)。将(C12)与(C8)代入(C6)可得

根据上式,mk与μk可以通过NCO(数字控制振荡器)对频率字累加计算得到。频率字定义为

其中p为NCO累加器的量化位数,fs=1/Ts为离散信号采样频率。因此(C13)可以重写为

其中m0与μ0为NCO累加器初值,定义为

下面对脉冲成形滤波器设计进行分析。对冲击响应h(t)等间隔分段,设分段间隔为T=γ-1T0,γ=2q(q=1,2,...)为符号内分段个数,q为设定的数值,小于p,q与滤波器的频率性能相关,q越大性能越好。将T=γ-1T0代入公式(1)可得

其中h(γi+ik′,μk′)=h[(γi+ik′)T+μk′T],γi+ik′=-γI,-γI+1,...,γI-1表示所有分段索引,

ik′=0,1,...,γ-1为符号内的分段索引;0≤μk′<1为段内小数间隔。

利用N次多项式对分段后的冲击响应近似

其中,多项式系数cn(γi+ik′)与bn(γi+ik′)满足下式关系

其中 cn(γi+ik′)本身满足对称性

cn(γi+ik′)=(-1)ncn(-(γi+ik′)-1)(8)

根据拉格朗日插值定理,系数bn(γi+ik′)可以通过下式计算得到

B=HA(9)

其中

B=[bn(γi+ik′)],H=[hn(γi+ik′)],A=[an(m)]T(10)

其中hn(γi+ik′)=h(γi+ik′,n/N),γi+ik′和m为矩阵的行索引,n为矩阵的列索引,系数an(m)可以通过下式得到

上式等号右侧为拉格朗日插值的N次插值基函数,通过等号左右变量μk′对应次幂系数相等,从而得到an(m)。

将公式(6)代入公式(4)中,可得基于多项式的插值滤波器Farrow结构的数学表达式

其中

为并行FIR滤波器,共N+1个FIR滤波器并行,其传递函数为

根据(13),

C(n,ik″)={cn(-γi+ik″)|i=-I,-I+1,...I-1}为当前FIR滤波器运算所需的滤波器系数,其相当于滤波器Cn(z)的γ级多项分解的初相为ik″的多项单元。用矩阵C(n)表示滤波器Cn(z)多相分解的所有初相的多项单元,可得并行FIR滤波器的系数矩阵为:

其中C(n)每一行为一个多项单元,可见C(n)包括了所有的滤波器系数。将C(n)上下平均分割为两部分:Cl(n)与Cr(n),根据对称性(8),Cr(n)可以由(-1)nCl(n)旋转180°得到。因此,在存储时,只需要记录系数矩阵Cl(n)就可得到滤波器所需的所有系数,从而减少了一半的滤波器系数存储资源。

根据上述理论分析,成形滤波器系数设计步骤包括3步:

(1)选取合适的窗函数对成形滤波器冲击响应截断、平滑;

(2)对加窗后的冲击响应等间隔分段,每个符号内分段个数为γ;

(3)基于拉格朗日插值,用N阶多项式对分段后的冲击响应近似,并求解滤波器系数。

参数计算模块处理流程包括3个步骤:

(1)NCO累加器量化位数为p,根据 (pbit量化后结果)设置NCO累加器初值,根据 获得频率字FW[k],根据 对频率字FW[k]进行累加,计算得到mk,输出给存储器,并利用 计算得到μk(pbit量化后结果),输出给成形滤波器模块,其中,R0=1/T0为已知的符号速率,Rd[l]为符号多普勒频率,fs为模拟频率;

(2)存储器根据接收的基本点索引mk,查表后得到符号x[mk],输出给成形滤波器模块;

(3)累加器内容μk高qbit作为参数i'k(qbit量化结果),μk低p-qbit作为参数μ'k(p-qbit量化结果)。

成形滤波器模块步骤包括6个步骤:

(1)成形滤波器模块接收存储器输出的符号x[mk],并保存在基本FIR滤波器中的移位寄存器中;

(2)并行的N+1个FIR滤波器寻址接收参数ik′,其最高位MSB作为控制位,控制低q-1bit产生滤波器系数ROM的地址;当MSB为‘0’时,寻址控制子模块直接输出ik′的低q-1bit作为地址ik″;当MSB为1时,寻址控制子模块对i'k的低q-1bit逐位取反,再作为地址ik″输出;

(3)滤波器系数ROM存储滤波器系数Cl(n);根据寻址控制模块输出地址ik″,对ROM寻址,输出滤波器系数C(n,ik″);

(4)当MSB为‘0’时,系数控制子模块直接输出滤波器系数C(n,ik″)至基本FIR滤波器相应位置的乘法器上;当MSB为‘1’时,系数控制子模块将所有滤波器系数C(n,ik″)乘以(-1)n后输出至相反位置的基本FIR滤波器的乘法器上;

(5)基本FIR滤波器接收符号及滤波器系数C(n,ik″),进行滤波操作,输出v(n);

(6)并行的N+1个FIR滤波器输出结果v(n),再与参数μk进行加权求和处理,最终输出高动态脉冲成形信号yd[k]。

装置:

本发明包括:参数计算模块以及成形滤波器模块。其中成形滤波器模块的设计是本发明的核心。包括参数计算模块与成形滤波器模块;参数计算模块包括上位机、NCO累加器、存储器与参数解算模块;成形滤波器模块包括并行的N+1个FIR滤波器模块与加权求和模块;每个FIR滤波器模块又包括寻址控制子模块、参数控制子模块、滤波器系数ROM以及基本FIR滤波器。

上位机用于接收自外部的符号速率R0,符号多普勒速率Rd[l]以及运动初始距离d0,计算得到频率字FW[k]与NCO累加器初值m0、μ0,将其输出给NCO模块;

其中p为NCO累加器的量化位数,R0=1/T0为符号速率,Rd[l]为符号多普勒频率,fs为模拟时钟频率,k为频率字索引。

NCO累加器用于接收自上位机的累加器初值m0、μ0及频率字FW[k]并进行累加,获得基本点索引mk和小数间隔μk,将基本点索引mk输出给存储器,将小数间隔μk输出给参数解算模块;

存储器进一步根据接收的基本点索引mk读取存储的待传输信息的符号x[mk],输出给并行的FIR滤波器模块;

参数解算模块进一步根据接收到的pbit的小数间隔μk产生符号内分段索引ik′与段内小数间隔μk′;ik′为μk的高qbit,μk′为μk的低p-qbit;将符号内分段索引ik′输出给各FIR滤波器模块,将段内小数间隔μk′输出给加权求和模块;

FIR滤波器模块中的寻址控制子模块根据接收到的符号内分段索引ik′产生地址ik″至滤波器系数ROM;当符号内分段索引ik′最高位(MSB)为‘0’时,输出ik′的低q-1bit作为地址ik″;当符号内分段索引ik′最高位(MSB)为‘1’时,对ik′的低q-1bit求反作为地址ik″;

FIR滤波器模块的滤波器系数ROM存储系数Cl(n),根据所接收到的地址ik″产生相应的滤波器系数C(n,ik″),并输出给系数控制子模块;

FIR滤波器模块的系数控制子模块根据接收到的符号内分段索引ik′的MSB以及滤波器系数C(n,ik″),产生基本FIR滤波器所需的相应乘法器上的滤波器系数;当ik′的MSB为‘0’时,将滤波器系数C(n,ik″)直接输出至基本FIR滤波器相应位置的乘法器上;当ik′的MSB为‘1’时,将滤波器系数C(n,ik″)乘以(-1)n后输出至基本FIR滤波器相反位置的乘法器上;

FIR滤波器模块内的基本FIR滤波器根据接收到的信息符号x[mk]以及滤波器系数C(n,ik″),经过滤波运算输出结果v(n)至加权求和模块;

加权求和模块根据接收到的并行FIR滤波器的输出v(n),经过加权求和运算,得到最终的离散高动态脉冲成形信号yd[k];

综上所述,以上仅为本发明的较佳实施例而已,并非用于限定本发明的保护范围。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

一种高动态脉冲成形信号模拟方法和装置专利购买费用说明

![]()

Q:办理专利转让的流程及所需资料

A:专利权人变更需要办理著录项目变更手续,有代理机构的,变更手续应当由代理机构办理。

1:专利变更应当使用专利局统一制作的“著录项目变更申报书”提出。

2:按规定缴纳著录项目变更手续费。

3:同时提交相关证明文件原件。

4:专利权转移的,变更后的专利权人委托新专利代理机构的,应当提交变更后的全体专利申请人签字或者盖章的委托书。

Q:专利著录项目变更费用如何缴交

A:(1)直接到国家知识产权局受理大厅收费窗口缴纳,(2)通过代办处缴纳,(3)通过邮局或者银行汇款,更多缴纳方式

Q:专利转让变更,多久能出结果

A:著录项目变更请求书递交后,一般1-2个月左右就会收到通知,国家知识产权局会下达《转让手续合格通知书》。

动态评分

0.0