专利摘要

本发明公开了一种混合模式AGC环路,属于电子技术领域。所述AGC环路包括VGA模块、峰值检测器、速度可变积分器、比较器、计数器、阈值控制模块和增益控制器;VGA模块与峰值检测器、速度可变积分器和增益控制器相连;峰值检测器与VGA模块和速度可变积分器相连;阈值控制器与速度可变积分器相连;速度可变积分器与峰值检测器、阈值控制器、VGA模块和比较器相连;比较器与计数器和速度可变积分器相连;计数器与比较器和增益控制器相连;增益控制器与计数器和VGA模块相连。本发明通过对差分中频信号增益进行模拟和数字双重模式控制,使得VGA模块的输出信号幅度不随其输入信号变化而变化;AGC环路电路结构简单且灵活。

权利要求

1.一种混合模式AGC环路,其特征在于,所述AGC环路包括VGA模块、峰值检测器、速度可变积分器、比较器、计数器、阈值控制模块和增益控制器;

所述VGA模块,与所述峰值检测器、速度可变积分器和增益控制器相连,用于接收外部输入信号,并根据所述速度可变积分器输出控制信号的大小对输入信号进行放大,将放大后的输入信号发送给所述峰值检测器,以及接收所述增益控制器输出的控制信号;

所述峰值检测器,与所述VGA模块和速度可变积分器相连,用于检测所述VGA模块发送的输出信号的峰值大小,并将峰值发送给所述速度可变积分器;

所述阈值控制器,与所述速度可变积分器相连,用于在外部控制信号的控制下,选择输出不同的阈值;

所述速度可变积分器,与所述峰值检测器、阈值控制器、VGA模块和比较器相连,用于在对阈值和检测到的信号峰值比较后,进行正/负积分,并输出控制信号;

所述比较器,与所述计数器和速度可变积分器相连,用于比较所述控制信号与外部比较信号的大小,并根据比较结果发送控制信号给所述计数器;

所述计数器,与所述比较器和增益控制器相连,用于根据所述比较器发送的控制信号进行计数,并将计数结果发送给所述增益控制器;

所述增益控制器,与所述计数器和VGA模块相连,用于根据所述计数器发送的计数结果,向所述VGA模块发送表示增加增益或降低增益的控制信号。

2.如权利要求1所述的混合模式AGC环路,其特征在于,所述VGA模块包括信号输入端,信号输出端和控制信号输入端;所述信号输入端输入差分中频信号,所述控制信号输入端输入的控制信号为模拟增益控制信号或数字增益控制信号。

3.如权利要求1所述的混合模式AGC环路,其特征在于,所述VGA模块由多个数字放大子单元和一个模拟放大子单元组成;一个数字放大子单元的输入端与所述VGA模块的信号输入端相连;每个数字放大子单元彼此相互连接,并且最后一个数字放大子单元的输出端与所述模拟放大子单元的输入端相连;所述模拟放大子单元的输出端与所述VGA模块的信号输出端相连。

4.如权利要求1所述的混合模式AGC环路,其特征在于,所述峰值检测器包括信号输入端和信号输出端;所述信号输入端与所述VGA模块的信号输出端相连;所述峰值检测器通过所述信号输出端将峰值信息发送给所述速度可变积分器。

5.如权利要求1所述的混合模式AGC环路,其特征在于,所述阈值控制器包括控制信号输入端和输出端;所述控制信号输入端与外部控制信号相连,所述输出端输出不同的阈值。

6.如权利要求1所述的混合模式AGC环路,其特征在于,所述速度可变积分器包括控制信号输入端、阈值输入端、峰值输入端和积分输出端;所述控制信号输入端用于选择不同的积分常数;所述峰值输入端和阈值输入端的大小,用于确定积分的方向。

7.如权利要求1所述的混合模式AGC环路,其特征在于,所述比较器包括第一比较器和第二比较器;所述第一比较器和第二比较器分别包括两个输入端和一个输出端;一个输入端接外部输入信号,另一个输入端与所述速度可变积分器的积分输出端相连;所述第一比较器的输出端用于发送递增计数使能控制信号给所述计数器;所述第二比较器的输出端用于发送递减计数使能控制信号给所述计数器。

8.如权利要求7所述的混合模式AGC环路,其特征在于,所述计数器包括第一计数器和第二计数器;所述第一计数器和第二计数器分别包括输入端、时钟输入端和信号输出端;所述第一计数器的输入端与所述第一比较器的输出端相连;所述第二计数器的输入端与所述第二比较器的输出端相连;所述时钟输入端接外部时钟信号;所述第一计数器根据其输入端的输入信号的高低电平,来确定是否递增计数,并把计数结果发送给所述增益控制器;所述第二计数器根据其输入端的输入信号的高低电平,来确定是否递减计数,并把计数结果发送给所述增益控制器。

9.

如权利要求1所述的混合模式AGC环路,其特征在于,所述增益控制器包括输入端和输出端;所述增益控制器根据所述输入端的输入大小,并进行逻辑运算,向所述VGA模块发送表示增加增益或降低增益的控制信号。

10.如权利要求1或8所述的混合模式AGC环路,其特征在于,所述表示增加增益或降低增益的控制信号为N位增益控制字,其中N为自然数。

说明书

技术领域技术领域

本发明涉及电子技术领域,特别涉及一种混合模式AGC环路。

技术背景背景技术

自动增益控制技术(AGC,Automatic Gain Control)广泛地应用于各类电子系统中,用于增大电子系统的动态范围。一个AGC主要由可变增益放大器(VGA,Variable GainAmplifier)和检测控制电路两部分组成;检测控制电路用于检测VGA输出信号的幅度,并通过一定的算法产生控制信号来调整VGA的输出增益,使VGA输出信号的幅度不随其输入而变化。现有技术中,检测控制电路有两种实现方法:其一,是采用模拟方法检测VGA输出信号的峰值,并对峰值信号进行低通滤波及放大后,反馈回VGA,进而控制VGA输出信号的增益;其二,是采用数字方法检测VGA输出信号的峰值,并对峰值信号进行一定处理后,产生数字控制量,来调整VGA的输出信号增益。

但是,上述两种检测控制电路的实现方法都存在缺陷;首先,模拟检测控制方法难以实现较宽增益范围的控制,并且AGC速度较慢;其次,数字检测方法虽然可以获得较宽增益范围的控制,但是如果电子系统没有A/D转换器,那么AGC是无法实现的。

发明内容发明内容

为了解决模拟检测控制方法无法实现较宽增益范围的控制,AGC速度慢,以及数字检测方法有时无法实现AGC等问题,本发明提供了一种混合模式AGC环路,所述AGC环路包括VGA模块、峰值检测器、速度可变积分器、比较器、计数器、阈值控制模块和增益控制器;

所述VGA模块,与所述峰值检测器、速度可变积分器和增益控制器相连,用于接收外部输入信号,并根据所述速度可变积分器输出控制信号的大小对输入信号进行放大,将放大后的输入信号发送给所述峰值检测器,以及接收所述增益控制器输出的控制信号;

所述峰值检测器,与所述VGA模块和速度可变积分器相连,用于检测所述VGA模块发送的输出信号的峰值大小,并将峰值发送给所述速度可变积分器;

所述阈值控制器,与所述速度可变积分器相连,用于在外部控制信号的控制下,选择输出不同的阈值;

所述速度可变积分器,与所述峰值检测器、阈值控制器、VGA模块和比较器相连,用于在对阈值和检测到的信号峰值比较后,进行正/负积分,并输出控制信号;

所述比较器,与所述计数器和速度可变积分器相连,用于比较所述控制信号与外部比较信号的大小,并根据比较结果发送控制信号给所述计数器;

所述计数器,与所述比较器和增益控制器相连,用于根据所述比较器发送的控制信号进行计数,并将计数结果发送给所述增益控制器;

所述增益控制器,与所述计数器和VGA模块相连,用于根据所述计数器发送的计数结果,向所述VGA模块发送表示增加增益或降低增益的控制信号。

所述VGA模块包括信号输入端,信号输出端和控制信号输入端;所述信号输入端输入差分中频信号,所述控制信号输入端输入的控制信号为模拟增益控制信号或数字增益控制信号。

所述VGA模块由多个数字放大子单元和一个模拟放大子单元组成;一个数字放大子单元的输入端与所述VGA模块的信号输入端相连;每个数字放大子单元彼此相互连接,并且最后一个数字放大子单元的输出端与所述模拟放大子单元的输入端相连;所述模拟放大子单元的输出端与所述VGA模块的信号输出端相连。

所述峰值检测器包括信号输入端和信号输出端;所述信号输入端与所述VGA模块的信号输出端相连;所述峰值检测器通过所述信号输出端将峰值信息发送给所述速度可变积分器。

所述阈值控制器包括控制信号输入端和输出端;所述控制信号输入端与外部控制信号相连,所述输出端输出不同的阈值。

所述速度可变积分器包括控制信号输入端、阈值输入端、峰值输入端和积分输出端;所述控制信号输入端用于选择不同的积分常数;所述峰值输入端和阈值输入端的大小,用于确定积分的方向。

所述比较器包括第一比较器和第二比较器;所述第一比较器和第二比较器分别包括两个输入端和一个输出端;一个输入端接外部输入信号,另一个输入端与所述速度可变积分器的积分输出端相连;所述第一比较器的输出端用于发送递增计数使能控制信号给所述计数器;所述第二比较器的输出端用于发送递减计数使能控制信号给所述计数器。

所述计数器包括第一计数器和第二计数器;所述第一计数器和第二计数器分别包括输入端、时钟输入端和信号输出端;所述第一计数器的输入端与所述第一比较器的输出端相连;所述第二计数器的输入端与所述第二比较器的输出端相连;所述时钟输入端接外部时钟信号;所述第一计数器根据其输入端的输入信号的高低电平,来确定是否递增计数,并把计数结果发送给所述增益控制器;所述第二计数器根据其输入端的输入信号的高低电平,来确定是否递减计数,并把计数结果发送给所述增益控制器。

所述增益控制器包括输入端和输出端;所述增益控制器根据所述输入端的输入大小,并进行逻辑运算,向所述VGA模块发送表示增加增益或降低增益的控制信号。

所述表示增加增益或降低增益的控制信号为N位增益控制字,其中N为自然数。

有益效果:本发明通过VGA模块、速度可变积分器和增益控制器,对差分中频信号增益进行模拟和数字双重模式控制,使得VGA模块的输出信号幅度不随其输入信号变化而变化;本发明提供的AGC环路的电路结构简单且灵活,AGC工作速度可以进行选择,从而可以满足多种系统的要求。

附图说明附图说明

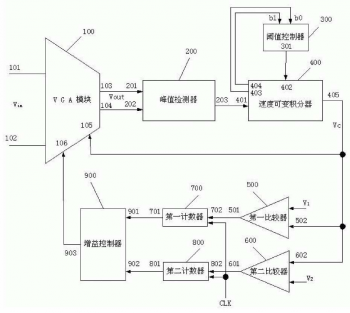

图1是本发明实施例提供的AGC环路电路原理结构示意图;

图2是本发明实施例VGA模块的内部电路原理结构示意图;

图3是本发明实施例速度可变积分器的电路原理结构示意图;

图4是本发明实施例混合模式AGC环路的计算机仿真结果曲线图。

具体实施方式具体实施方式

为使本发明的目的、技术方案和优点更加清楚,下面将结合附图对本发明实施方式作进一步地详细描述。

参见图1,本发明实施例提供了一种混合模式AGC环路,包括VGA模块100、峰值检测器200、速度可变积分器400、第一比较器500、第二比较器600、第一计数器700、第二计数器800、阈值控制模块300和增益控制器900;

VGA模块100,与峰值检测器200、速度可变积分器400和增益控制器900相连,用于接收外部输入信号,并根据速度可变积分器400输出控制信号(Vc)的大小对输入信号进行放大,将放大后的输入信号发送给峰值检测器200,以及接收增益控制器900输出的控制信号;

峰值检测器200,与VGA模块100和速度可变积分器400相连,用于检测VGA模块100发送的输出信号的峰值大小,并将峰值发送给速度可变积分器400;

阈值控制器300,与速度可变积分器400相连,用于在外部控制信号的控制下,选择输出不同的阈值;

速度可变积分器400,与峰值检测器200、阈值控制器300、VGA模块100、第一比较器500和第二比较器600相连,用于在对阈值和检测到的信号峰值比较后,进行正/负积分,并输出控制信号Vc;

第一比较器500,与第一计数器700和速度可变积分器400相连,用于比较控制信号Vc与外部比较信号V1的大小,并根据比较结果发送控制信号给第一计数器700;

第二比较器600,与第二计数器800和速度可变积分器400相连,用于比较控制信号Vc与外部比较信号V2的大小,并根据比较结果发送控制信号给第一计数器800;

第一计数器700,与第一比较器500和增益控制器900相连,用于根据第一比较器500发送的控制信号进行计数,并将计数结果发送给增益控制器900;

第二计数器800,与第二比较器600和增益控制器900相连,用于根据第二比较器600发送的控制信号进行计数,并将计数结果发送给增益控制器900;

增益控制器900,与第一计数器700、第二计数器800和VGA模块100相连,用于根据第一计数器700和第二计数器800发送的计数结果,向VGA模块100发送表示增加增益或降低增益的控制信号。

其中,VGA模块100包括信号输入端101和102,信号输出端103和104,以及控制信号输入端105和106;信号输入端101和102输入差分中频信号;控制信号输入端105输入的控制信号Vc为模拟增益控制信号;控制信号输入端106输入的控制信号为数字增益控制信号;在实际应用中,当AGC用于接收机系统时,信号输入端101和102与混频器相连,即信号输入端输入的信号是混频之后的差分中频信号;VGA模块100根据控制信号的大小来确定对输入信号进行放大的倍数,从而将放大后的信号输出给峰值检测器200;图2示出了VGA模块100的内部电路原理结构示意图,假设信号输入端101和102的输入信号为Vin,信号输出端103和104的输出信号为Vout,信号输入端与混频器的输出端相连,VGA模块100由四个数字放大子单元(A1、A2、A3、A4)和一个模拟放大子单元(A5)组成,数字放大子单元由增益控制器900发送的数字增益控制信号(D0、D1、D2和D3)控制其增益大小,模拟放大子单元由速度可变积分器400发送的控制信号Vc控制其增益大小;数字放大子单元A1、A2、A3和A4的增益范围可以根据实际系统要求设置为0~10dB,或者其他增益范围;数字增益控制信号D0、D1、D2和D3的位数也可以根据实际系统要求进行设置;模拟放大子单元A5的增益和控制信号Vc的大小成正比,可以通过Vc进行动态调整,其增益范围可以根据实际系统要求设置。

其中,峰值检测器200包括信号输入端201和202,以及信号输出端203;信号输入端201和202分别与VGA模块100的信号输出端103和104相连;峰值检测器200通过信号输出端203将峰值信息发送给速度可变积分器400。

其中,阈值控制器300包括控制信号输入端b1和b0,以及输出端301;控制信号输入端b1和b0与外部控制信号相连,输出端301输出不同的阈值,从而改变速度可变积分器400的积分速度。

其中,速度可变积分器400包括控制信号输入端403和404,阈值输入端402,峰值输入端401和积分输出端405;控制信号输入端403和404分别与阈值控制器300的控制信号输入端b0和b1相连,用于选择不同的积分常数,从而选择不同的积分速度;峰值输入端401和阈值输入端402的大小可以确定积分的方向,从而使输出的控制信号Vc增加或减小;图3示出了速度可变积分器400的电路原理结构示意图,阈值输入端402与阈值控制器300的输出端301相连,峰值输入端401与峰值检测器200的信号输出端203相连,速度可变积分器400根据峰值输入端401和阈值输入端402的大小,以及控制信号b1和b0的选择来确定正积分或负积分,从而确定积分速度。

其中,第一比较器500包括输入端V1和502,以及输出端501;输入端V1接外部输入信号,输入端502与速度可变积分器400的积分输出端405相连;第一比较器500根据输入端V1和502的大小,发送递增计数使能控制信号给第一计数器700。

其中,第二比较器600包括输入端V2和602,以及输出端601;输入端V2接外部输入信号,输入端602与速度可变积分器400的积分输出端405相连;第二比较器600根据输入端V2和602的大小,发送递减计数使能控制信号给第二计数器800。

其中,第一计数器700包括输入端702、时钟输入端和信号输出端701;输入端702与第一比较器500的输出端501相连;时钟输入端接外部时钟信号CLK;第一计数器700根据输入端702的输入信号的高低电平,来确定是否递增计数,并把计数结果发送给增益控制器900。

其中,第二计数器800包括输入端802、时钟输入端和信号输出端801;输入端802与第二比较器600的输出端601相连;时钟输入端接外部时钟信号CLK;第二计数器800根据输入端802的输入信号的高低电平,来确定是否递减计数,并把计数结果发送给增益控制器900。

其中,增益控制器900包括输入端901和902,以及输出端103;增益控制器900根据输入端901和902的输入大小,并进行逻辑运算,向VGA模块100发送表示增加增益或降低增益的控制信号。在实际应用中,控制信号可以为N位增益控制字,其中N为自然数。

本发明实施例提供的混合模式AGC环路的工作原理是:峰值检测器200检测VGA模块100当前时刻的输入幅度,并将峰值输入到速度可变积分器400;速度可变积分器400比较输入信号401和402的大小,如果401大于402,则根据控制信号b0和b1的选择模式进行负积分,否则,则进行正积分,并输出积分控制信号Vc;积分控制信号Vc一方面调整VGA模块100的增益,另一方面被发送给第一比较器500和第二比较600,如果Vc的调整可以使VGA模块100达到输出幅度的要求,则AGC达到了目的;如果Vc的调整不能使VGA模块100达到输出幅度的要求,则通过第一比较器500输出递增信号或第二比较器600输出递减信号,使第一计数器700开始递增计数或使第二计数器800开始递减计数,并将计数结果发送给增益控制器900;增益控制器900根据输入的计数结果,进行逻辑运算,输出调整增益控制字,进而控制VGA模块100的增益。图4是本发明实施例混合模式AGC环路的计算机仿真结果,其中输入信号VT(/IN)为一个连续地且有微小变化的弱信号,VT(/OP)为VGA模块100输出的波形,VT(/Vtrl)为速度可变积分器400输出的控制信号Vc的波形。

本发明实施例通过VGA模块、速度可变积分器和增益控制器,对差分中频信号增益进行模拟和数字双重模式控制,使得VGA模块的输出信号幅度不随其输入信号变化而变化;本发明提供的AGC环路的电路结构简单且灵活,AGC工作速度可以进行选择,从而可以满足多种系统的要求。

以上所述仅为本发明的较佳实施例,并不用以限制本发明,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

一种混合模式AGC环路专利购买费用说明

![]()

Q:办理专利转让的流程及所需资料

A:专利权人变更需要办理著录项目变更手续,有代理机构的,变更手续应当由代理机构办理。

1:专利变更应当使用专利局统一制作的“著录项目变更申报书”提出。

2:按规定缴纳著录项目变更手续费。

3:同时提交相关证明文件原件。

4:专利权转移的,变更后的专利权人委托新专利代理机构的,应当提交变更后的全体专利申请人签字或者盖章的委托书。

Q:专利著录项目变更费用如何缴交

A:(1)直接到国家知识产权局受理大厅收费窗口缴纳,(2)通过代办处缴纳,(3)通过邮局或者银行汇款,更多缴纳方式

Q:专利转让变更,多久能出结果

A:著录项目变更请求书递交后,一般1-2个月左右就会收到通知,国家知识产权局会下达《转让手续合格通知书》。

动态评分

0.0